### ES0003 Errata Sheet

#### AT32F435/437 device limitations

## **Device identification**

This errata sheet applies to ARTERY AT32F435/437 microcontrollers based on an ARM™ 32-bit Cortex®-M4 core.

The full list of part numbers is shown in Table 2. The products are identifiable as shown in table 1:

by the revision code marked below the lot number on the device package

#### Table 1. Device identification

| Part number  | Revision code printed on device |  |

|--------------|---------------------------------|--|

| AT32F435/437 | "A"                             |  |

| A152F455/457 | "B"                             |  |

|              |                                 |  |

The Bit [78:76] Mask\_Version in the device capacity and unique ID (UID base address 0x1FFF F7E8) shows the revision code of the device. That is, the bit [6:4] at the address 0x1FFF7F1 can be used to get the revision code, for example Revision A: 0b000 Revision B: 0b001

2. Refer to Chapter 2 for details on how to identify the revision code on the different packages.

| Device   | Flash memory | Part number                                                                |

|----------|--------------|----------------------------------------------------------------------------|

| AT32F435 | 4032 KB      | AT32F435ZMT7, AT32F435VMT7,<br>AT32F435RMT7, AT32F435CMT7,<br>AT32F435CMU7 |

|          | 1024 KB      | AT32F435ZGT7, AT32F435VGT7,<br>AT32F435RGT7, AT32F435CGT7,<br>AT32F435CGU7 |

|          | 448 KB       | AT32F435ZDT7, AT32F435VDT7<br>AT32F435RDT7, AT32F435CDT7<br>AT32F435CDU7   |

|          | 256 KB       | AT32F435ZCT7, AT32F435VCT7,<br>AT32F435RCT7, AT32F435CCT7,<br>AT32F435CCU7 |

| AT32F437 | 4032 KB      | AT32F437ZMT7, AT32F437VMT7,<br>AT32F437RMT7                                |

|          | 1024 KB      | AT32F437ZGT7, AT32F437VGT7,<br>AT32F437RGT7                                |

|          | 448 KB       | AT32F437ZDT7 , AT32F437VDT7<br>AT32F437RDT                                 |

|          | 256 KB       | AT32F437ZCT7, AT32F437VCT7,<br>AT32F437RCT7                                |

#### Table 2. Device summary

## Contents

| 1 | AT32F435/437 device limitations |       |                                                                                |       |

|---|---------------------------------|-------|--------------------------------------------------------------------------------|-------|

|   | 1.1                             | CAN   |                                                                                | 6     |

|   |                                 | 1.1.1 | Bit stuffing error causes the next data out-of-order during CAN communication. | 6     |

|   |                                 | 1.1.2 | Failed to filter RTR bit of standard frame in 32-bit identifier mask mode      | 9     |

|   |                                 | 1.1.3 | CAN sends unexpected messages in case of narrow pulse disturbance on BS2       | 10    |

|   |                                 | 1.1.4 | Fail to cancel mailbox transmit command when CAN bus disconnected              | 10    |

|   | 1.2                             | DMAN  | /UX                                                                            | 11    |

|   |                                 | 1.2.1 | Setting EVTGEN bit for DMAMUX synchronization                                  | 11    |

|   | 1.3                             | EDMA  | ۱                                                                              | 11    |

|   |                                 | 1.3.1 | Preemption priority between data streams failed in EDMA linked list mode       | 11    |

|   | 1.4                             | I2S   |                                                                                | 12    |

|   |                                 | 1.4.1 | I2S communication failed when SPITI mode and 3-divided frequency are en        | abled |

|   |                                 |       | simultaneously                                                                 | 12    |

|   |                                 | 1.4.2 | First data error in I2S PCM standard long frame receive-only mode              | 12    |

|   |                                 | 1.4.3 | UDR flag is set in I2S slave transmission mode and discontinuous communi-      |       |

|   |                                 |       | state                                                                          | 13    |

|   |                                 | 1.4.4 | Data reception error when I2S 24-bit data is packed into 32-bit format         | 13    |

|   | 1.5                             | PWC.  |                                                                                | 13    |

|   |                                 | 1.5.1 | Unable to wakeup Deepsleep mode after AHB frequency division                   | 13    |

|   |                                 | 1.5.2 | Unable to select system clock source after waking up Deepsleep mode            | 13    |

|   |                                 | 1.5.3 | SWEF flag is set when enabling a standby-mode wakeup pin                       | 14    |

|   |                                 | 1.5.4 | Precautions on LDO use                                                         | 15    |

|   |                                 | 1.5.5 | Entering Deepsleep mode during DMA/EDMA transfer causes data transfer error    | or15  |

|   | 1.6                             | SDRA  | M                                                                              | 16    |

|   |                                 | 1.6.1 | SDRAM read error in burst read mode                                            | 16    |

|   |                                 | 1.6.2 | SDRAM low-power mode limitations                                               | 16    |

|   |                                 | 1.6.3 | SDRAM and other XMC static memory usage limitations                            | 16    |

|   | 1.7                             | SPI   |                                                                                | 17    |

|   |                                 | 1.7.1 | CS pulse flag is set in SPI slave TI mode                                      | 17    |

|   |                                 | 1.7.2 | CS failing edge not synchronized in SPI slave hardware CS mode                 | 17    |

|   |                                 | 1.7.3 | Unable to clear data reception DMA transfer request by reading DT register     | 17    |

|   | 1.8                             | QSPI. |                                                                                |       |

## **Y5-17:**

## AT32F435/437 Device Limitations

|              | 1.8.1  | QSPI access error when QSPI is not initialized as an XIP port          | 18 |

|--------------|--------|------------------------------------------------------------------------|----|

|              | 1.8.2  | Counter error in QSPI XIP port D mode write configuration              | 18 |

|              | 1.8.3  | QSPI Cache usage limitations                                           | 18 |

|              | 1.8.4  | QSPI clock polary selection limitation                                 | 19 |

|              | 1.8.5  | DMA P2M mode usage condition in QSPI command port mode                 | 19 |

|              | 1.8.6  | Excess dummy clock sent after read operation in QSPI command port mode | 19 |

| 1.9          | USAR   | ат                                                                     | 20 |

|              | 1.9.1  | USART ROERR flag is set exceptionally                                  | 20 |

| 1.10         | ADVT   | M                                                                      | 20 |

|              | 1.10.1 | How to clear TMR-triggered DAM requests                                | 20 |

|              | 1.10.2 | TMR overrun in encoder mode counter                                    | 21 |

|              | 1.10.3 | Break input failed when TMREN=0                                        | 21 |

| 1.11         | ERTC   |                                                                        | 22 |

|              | 1.11.1 | Writing ERTC occupies APB for 4 ERTC clock cyles                       | 22 |

|              |        |                                                                        |    |

| Revi         | sion c | ode on device marking                                                  | 23 |

| <b>D</b> - 7 |        |                                                                        | •  |

| DOCI         | ument  | revision history                                                       | 24 |

2

3

## List of tables

| Table 1. Device identification         | 1   |

|----------------------------------------|-----|

| Table 2. Device summary                | 1   |

| Table 2. Summary of device limitations | 5   |

| Table 4. Document revision history     | .24 |

## 1 AT32F435/437 device limitations

Table 3 gives a list of limitations that have been identified so far on the AT32F435/437 devices.

| Section    | Description                                                                                        | Revision | Revision             |

|------------|----------------------------------------------------------------------------------------------------|----------|----------------------|

| Section    | Description                                                                                        |          | В                    |

| 1.1 CAN    | 1.1.1 Bit stuffing error causes the next data out-of-order during CAN communication.               | Fail     | Fixed                |

|            | 1.1.2 Failed to filter RTR bit of standard frame in 32-bit identifier mask mode.                   | Fail     | Fixed                |

|            | 1.1.3 CAN sends unexpected messages in case of narrow pulse disturbance on BS2.                    | Fail     | Fixed                |

|            | 1.1.4 Fail to cancel mailbox transmit command when CAN bus disconnected                            | Fail     | Fail                 |

| 1.2 DMAMUX | 1.2.1 Setting EVTGEN bit for DMAMUX synchronization.                                               | Fail     | Fail                 |

| 1.3 EDMA   | 1.3.1 Preemption priority between data streams failed in EDMA linked list mode                     | Fail     | Fail                 |

|            | 1.4.1 I2S communication failed when SPITI mode and 3-divided frequency are enabled simultaneously. | Fail     | Fail                 |

|            | 1.4.2 First data error in I2S PCM standard long frame receive-only mode.                           | Fail     | Fail                 |

| 1.4 I2S    | 1.4.3 UDR flag is set in I2S slave transmission mode and discontinuous communication state.        | Fail     | Fail                 |

|            | 1.4.4 Data reception error when I2S 24-bit data is packed into 32-bit format.                      | Fail     | Fail                 |

|            | 1.5.1 Unable to wakeup Deepsleep mode after AHB frequency division.                                | Fail     | Fail                 |

|            | 1.5.2 Unable to select system clock source after waking up Deepsleep mode                          | Fail     | Fixed                |

| 1.5 PWC    | 1.5.3 SWEF flag is set when enabling a standby-mode wakeup pin.                                    | Fail     | Fail                 |

|            | 1.5.4 Precautions on LDO use                                                                       | Fail     | Fail                 |

|            | 1.5.5 Entering Deepsleep mode during DMA/EDMA transfer causes data transfer error                  | Fail     | Fail                 |

|            | 1.6.1 SDRAM read error in burst read mode.                                                         | Fail     | Fixed                |

| 1.6 SDRAM  | 1.6.2 SDRAM low-power mode limitations.                                                            | Fail     | Fail                 |

|            | 1.6.3 SDRAM and other XMC static memory usage limitations.                                         | Fail     | Fixed <sup>(1)</sup> |

|            | 1.7.1 CS pulse flag is set in SPI slave TI mode                                                    | Fail     | Fail                 |

| 1.7 SPI    | 1.7.2 CS failing edge not synchronized in SPI slave hardware CS mode                               | Fail     | Fail                 |

|            | 1.7.3 Unable to clear data reception DMA transfer request by reading DT register                   | Fail     | Fail                 |

|            | 1.8.1 QSPI access error when QSPI is not initialized as an XIP port                                | Fail     | Fixed                |

|            | 1.8.2 Counter error in QSPI XIP port D mode write configuration                                    | Fail     | Fixed                |

| 1.8 QSPI   | 1.8.3 QSPI Cache usage limitations                                                                 | Fail     | Fixed                |

|            | 1.8.4 QSPI clock polary selection limitation                                                       | Fail     | Fixed                |

|            | 1.8.5 DMA P2M mode usage condition in QSPI command port mode                                       | Fail     | Fail                 |

|            | 1.8.6 Excess dummy clock sent after read operation in QSPI command port mode                       | Fail     | Fail                 |

| 1.9 USART  | 1.9.1 USART ROERR flag is set mistakenly                                                           | Fail     | Fixed                |

|            | 1.10.1 How to clear TMR-triggered DAM requests.                                                    | Fail     | Fixed                |

| 1.10 ADVTM | 1.10. 2 TMR overrun in encoder mode counter.                                                       | Fail     | Fail                 |

|            | 1.10.3 Break input failed when TMREN=0                                                             | Fail     | Fail                 |

| 1.11 ERTC  | 1.11.1 Writing ERTC occupies APB for 4 ERTC clock cyles                                            | Fail     | Fail                 |

#### Table 3. Summary of device limitations

(1) For Revision B, SDRAM, XMC PSRAM, NOR FLASH and SRAM can be used at the same time but it should be noted that SDRAM must be initialized before use and SDRAM can not be set in Low-power mode. Other XMC static memories such as NAND and PC card cannot be used simultaneously.

## 1.1 CAN

# 1.1.1 Bit stuffing error causes the next data out-of-order during CAN communication

#### Description:

If a bit stuffing error occurs in the data filed during CAN communication due to external disturbance, CAN will stop receiving the current data frame and send an error to the bus, but the next data frame will be out of order while the subsequent messages are able to return to normal automatically.

Workaround:

#### Method 1:

Enable the CAN error interrupt (its priority must be set very high) corresponding to the interrupt number in the CAN error type record. Once a bit stuffing error is detected, reset CAN (only need reset CAN registers and relevant GPIOs, without resetting NVIC), and re-initialize CAN in the CAN error interrupt functions.

This method applies to the scenario where a quick CAN initialization is required in order to ensure a quick resume of CAN communication and avoid too much CAN data loss. Take a CAN1 as an example, its typical code as follows:

```

/* Enable CAN error interrupt corresponding to the last CAN error interrupt number and give very high

priority */

nvic_irq_enable(CAN1_SE_IRQn, 0x00, 0x00);

can_interrupt_enable(CAN1, CAN_ETRIEN_INT, TRUE);

can interrupt enable(CAN1, CAN EOIEN INT, TRUE);

/* Interrupt service functions */

void CAN1 SE IRQHandler(void)

{

__IO uint32_t err_index = 0;

if(can flag get(CAN1,CAN ETR FLAG) != RESET)

{

err_index = CAN1->ests & 0x70;

can flag clear(CAN1, CAN ETR FLAG);

if(err index == 0x0000010)

{

can reset(CAN1);

/* Call CAN initialization function */

}

}

```

#### Notes:

- a) CAN error interrupts should be given as very high priority;

- b) As it takes some time to finish CAN initialization, CAN's inability to resume communication immediately when an error occurs may cause loss of data.

#### Method 2:

Enable the CAN error interrupt (its priority must be set very high) corresponding to the interrupt number in the CAN error type record. Once a bit stuffing error is detected, reset CAN (only need reset CAN registers and relevant GPIOs, without resetting NVIC), record the reset event, and re-initialize CAN in other low-priority interrupts or main functions.

This method applies to the scenario where the CAN communication is unable to resume in time, but the CAN re-initialization must be performed in order not to affect the operations of other applications.

Take a CAN1 as an example, its typical code as follows:

```

/*Enable CAN error interrupt corresponding to the last CAN error interrupt number and give very high

priority*/

nvic_irq_enable(CAN1_SE_IRQn, 0x00, 0x00);

can interrupt enable(CAN1, CAN ETRIEN INT, TRUE);

can interrupt enable(CAN1, CAN EOIEN INT, TRUE);

/* Interrupt service functions*/

__IO uint32_t can_reset_index = 0;

void CAN1 SE IRQHandler(void)

{

__IO uint32_t err_index = 0;

if(can flag get(CAN1,CAN ETR FLAG) != RESET)

{

err index = CAN1->ests & 0x70;

can_flag_clear(CAN1, CAN_ETR_FLAG);

if(err index == 0x0000010)

{

can_reset(CAN1);

can_reset_index = 1;

}

}

}

```

Then the application polls whether "can\_reset\_index" is set or not at the desired place (in main functions, say). Call the CAN initialization function, if available.

#### Notes:

- a) CAN error interrupts should be given as very high priority;

- b) As it takes some time to finish CAN initialization, CAN's inability to resume communication immediately when an error occurs may cause loss of data.

## -17L=2A

#### Method 3:

Enable the CAN error interrupt (its priority must be set very high) corresponding to the interrupt number in the CAN error type record. Once a bit stuffing error is detected, forcibly send an invalid message with a very-high-priority identifier.

This method applies to the scenario where one doesn't want to spend time on CAN reset, all message identifiers on CAN bus are known, and each CAN node receives messages in accordance with the identifier filtering conditions.

Take a CAN1 as an example, its typical code as follows:

| /*Forcibly send a frame of invalid message with a very-high-priority identifier*/                                 |  |  |  |

|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| static void can transmit data(void)                                                                               |  |  |  |

| {                                                                                                                 |  |  |  |

| uint8_t transmit_mailbox;                                                                                         |  |  |  |

| can_tx_message_type tx_message_struct;                                                                            |  |  |  |

| tx_message_struct.standard_id = 0x0;                                                                              |  |  |  |

| tx_message_struct.extended_id = 0x0;                                                                              |  |  |  |

| tx_message_struct.id_type = CAN_ID_STANDARD;                                                                      |  |  |  |

| tx_message_struct.frame_type = CAN_TFT_DATA;                                                                      |  |  |  |

| tx_message_struct.dlc = 8;                                                                                        |  |  |  |

| tx_message_struct.data[0] = 0x00;                                                                                 |  |  |  |

| tx_message_struct.data[1] = 0x00;                                                                                 |  |  |  |

| tx_message_struct.data[2] = 0x00;                                                                                 |  |  |  |

| tx_message_struct.data[3] = 0x00;                                                                                 |  |  |  |

| tx_message_struct.data[4] = 0x00;                                                                                 |  |  |  |

| tx_message_struct.data[5] = 0x00;                                                                                 |  |  |  |

| tx_message_struct.data[6] = 0x00;                                                                                 |  |  |  |

| tx_message_struct.data[7] = 0x00;                                                                                 |  |  |  |

| can_message_transmit(CAN1, &tx_message_struct);                                                                   |  |  |  |

| }                                                                                                                 |  |  |  |

| /* Enable CAN error interrupt corresponding to the last CAN error interrupt number and give very high priority */ |  |  |  |

| nvic_irq_enable(CAN1_SE_IRQn, 0x00, 0x00);                                                                        |  |  |  |

| can_interrupt_enable(CAN1, CAN_ETRIEN_INT, TRUE);                                                                 |  |  |  |

| can_interrupt_enable(CAN1, CAN_EOIEN_INT, TRUE);<br>/* Interrupt service functions*/                              |  |  |  |

| void CAN1_SE_IRQHandler(void)                                                                                     |  |  |  |

| {                                                                                                                 |  |  |  |

| IO uint32_t err_index = 0;                                                                                        |  |  |  |

| if(can_flag_get(CAN1,CAN_ETR_FLAG) != RESET)                                                                      |  |  |  |

| {                                                                                                                 |  |  |  |

```

err_index = CAN1->ests & 0x70;

can_flag_clear(CAN1, CAN_ETR_FLAG);

if(err_index == 0x00000010)

{

can_transmit_data;

}

}

```

#### Notes:

}

- a) CAN error interrupts should be given as very high priority;

- b) This method is only applicable to the scenario where the transmit FIFO priority is determined by message identifiers;

- c) The identifier of the invalid message in this method is changeable. But its priority must be given the highest among the CAN bus, and it cannot be received as a normal message by other nodes.

- Revision: Revision B has fixed this issue.

# 1.1.2 Failed to filter RTR bit of standard frame in 32-bit identifier mask mode

Description:

When the CAN filter mode is configured in 32-bit identifier mask mode, the RTR bit (remote frame identifier) cannot be filtered effectively during a standard frame filtering.

When the following conditions are present, follow the "Workaround" to solve this problem:

- 1. Enable 32-bit wide identifier mask mode

- 2. Filter standard frames but not expect to receive remote frames that meet filtering conditions

- Workaround:

Method 1: By software. When filtering a standard frame in 32-bit wide identifier mask mode, the software is used to get the status of the RTR bit (remote frame identifier) and decide if this frame of message is of interest. For example:

```

void CAN1_RX0_IRQHandler(void)

{

can_rx_message_type rx_message_struct;

if(can_flag_get(CAN1,CAN_RF0MN_FLAG) != RESET)

{

can_message_receive(CAN1, CAN_RX_FIFO0, &rx_message_struct);

/* only store the data frame,discard the remote frame */

if((rx_message_struct.id_type == CAN_ID_STANDARD) && (rx_message_struct.frame_type ==

CAN_TFT_DATA))

{

/* user store the receive data */

}

}

}

```

}

Method 2: Use other filtering mode according to the needs, such as, 32-bit wide identifier list mode, 16-bit wide identifier mask mode or 16-bit wide identifier list mode.

• Revision: Revision B has fixed this issue.

# 1.1.3 CAN sends unexpected messages in case of narrow pulse disturbance on BS2

Description:

In case of a large amount of narrow pulses (pulse width less than 1tp) on CAN bus, the CAN nodes are likely to send unexpected messages, for instance, a data frame is sent as a remote frame, a standard frame as an extended one, or data phase error occurs.

Workaround:

Configure synchronization width RSAW = BTS2 segment width to avoid unexpected errors.

It should be noted that after RSAW =BTS2 is asserted, the CAN bus communication speed is reduced when there is a lot of disturbance on CAN bus.

```

static void can_configuration(void)

{

...

/* can baudrate, set baudrate = pclk/(baudrate_div *(3 + bts1_size + bts2_size)) */

can_baudrate_struct.baudrate_div = 12;

can_baudrate_struct.rsaw_size = CAN_RSAW_3TQ;

can_baudrate_struct.bts1_size = CAN_BTS1_8TQ;

can_baudrate_struct.bts2_size = CAN_BTS2_3TQ;

...

}

```

• Revision: Revision B has fixed this issue.

# 1.1.4 Fail to cancel mailbox transmit command when CAN bus disconnected

• Description:

As a node for data transmission, if the following two conditions are both present for CAN, it is not possible to clear or cancel a transmit command in a mailbox within CAN error passive interrupt, causing that the to-be-sent message command has not been canceled during the period of CAN bus being disconnected, and such message would be retransmitted after CAN bus communication resumes.

- 1. CAN bus (CANH/L) is disconnected intentially or accidentally

- 2. Auotmaitc retransmission feature is enabled

- Workaround:

Enable CAN error passive interrupt and disable its automatic retransmission before re-enabling automatic retransmission in the message transmit function, as shown below:

1) Enable error passive interrupt during CAN initialization

```

nvic_irq_enable(CAN1_SE_IRQn, 0x00, 0x00);

can_interrupt_enable(CAN1, CAN_EPIEN_INT, TRUE);

can_interrupt_enable(CAN1, CAN_EOIEN_INT, TRUE);

```

2) Disable automatic transmission feature in CAN error passive interrupt function

```

void CAN1_SE_IRQHandler(void)

{

if(can_flag_get(CAN1,CAN_EPF_FLAG) != RESET)

{

CAN1->mctrl |= (uint32_t)(1<<4);

can_flag_clear(CAN1, CAN_EPF_FLAG);

}

}</pre>

```

3) Re-enable automatic transmission feature in CAN message transmit function

```

CAN1->mctrl &= (uint32_t)~(1<<4);

```

Revision:

None.

#### 1.2 DMAMUX

### 1.2.1 Setting EVTGEN bit for DMAMUX synchronization

Description:

To use DMAMUX synchronization, the EVTGEN must be set to 1 in addition to SYCEN=1, otherwise the synchronization signal does not take effect.

Workaround:

Set the EVTGEN bit while configuring synchronization by software.

Revision: None.

#### 1.3 EDMA

## 1.3.1 Preemption priority between data streams failed in EDMA linked list mode

Description:

When more than one data streams are configured in linked list mode, the preemption priority between data streams becomes invalid.

Workaround:

None.

Revision: None.

## 1.4 I2S

# 1.4.1 I2S communication failed when SPITI mode and 3-divided frequency are enabled simultaneously

• Description:

If three-divided frequency feature and SPI TI mode are enabled simultaneously, I2S communication error would occur.

• Workaround:

This is an abnormal operation. Neither SPI TI mode nor three-divided frequency feature is applicable to I2S. They are forbidden in I2S.

• Revision: None.

# 1.4.2 First data error in I2S PCM standard long frame receive-only mode

• Description:

When the following three conditions are present for I2S, it is likely that the first data you receive is incorrect but the subsequent data can return to normal

The three conditions are as follows:

- 1. Set PCM long frame standard receive-only mode

- 2. I2SCPOL = 0

- 3. SCK remains high, which is abnormal, before I2S enable

- Workaround:

Pull up or pull down the SCK pin externally or internally, depending on the I2SCLKPOL configuration.

• Revision: None.

# 1.4.3 UDR flag is set in I2S slave transmission mode and discontinuous communication state

#### • Description:

The UDR flag is set in I2S slave transmit mode combined with discontinuous communication state, even if data have been written before the start of communication.

• Workaround:

For continuous communication, it is recommended to use DMA or interrupts for fast data transfer in I2S slave transmission mode according to the protocols.

• Revision: None.

# 1.4.4 Data reception error when I2S 24-bit data is packed into 32-bit format

• Description:

When I2S 24-bit data is packed into 32-bit frame format, the remaining 8 invalid CLK data would be received by the receiver as normal data.

• Workaround:

Method 1: Both the receiver and transmitter use the same way of packing 24-bit data into 32bit format.

Method 2: Discard these 8 invalid CLK data in this frame format using software.

Revision: None.

## 1.5 PWC

### 1.5.1 Unable to wakeup Deepsleep mode after AHB frequency division

• Description:

If AHB frequency is divided, no wakeup sources can wake up Deepsleep mode.

• Workaround:

Do not divide AHB frequency in Deepsleep mode.

Remove AHB frequency division before entering Deepsleep mode. Configure then the desired AHB frequency after waking up Deepsleep mode.

• Revision: None.

## 1.5.2 Unable to select system clock source after waking up Deepsleep mode

• Description:

When a wakeup source arrives at the moment while the Deepsleep mode is being entered, either HEXT or PLL could no longer be selected as the clock source of system clock.

- Workaround: After waking up Deepsleep mode, wait around 3 LICK clock cycles before starting system clock configuration.

- Revision: Revision B has fixed this issue.

#### 1.5.3 SWEF flag is set when enabling a standby-mode wakeup pin

#### • Description:

Before enabled, if a standby-mode wakeup pin were used as a GPIO push-pull output (high) or pull-up input, a SWEF flag would be set immediately once the pin is enabled.

Workaround:

If a standby-mode wakeup pin was used as a GPIO before, the IO then needs to be reinitialized to pull-down input or analog input before enabling the wakeup pin. For example:

```

gpio_init_type gpio_init_struct;

/* enable the wakeup pin clock */

crm_periph_clock_enable(CRM_GPIOA_PERIPH_CLOCK, TRUE);

/* set default parameter */

gpio_default_para_init(&gpio_init_struct);

/* configure wakeup pin as input with pull-down */

gpio_init_struct.gpio_drive_strength = GPIO_DRIVE_STRENGTH_STRONGER;

gpio_init_struct.gpio_out_type = GPIO_OUTPUT_PUSH_PULL;

gpio_init_struct.gpio_mode = GPIO_MODE_INPUT;

gpio_init_struct.gpio_pins = GPIO_PINS_0;

gpio_init_struct.gpio_pull = GPIO_PULL_DOWN;

gpio_init(GPIOA, &gpio_init_struct);

/* enable wakeup pin1-pa0 */

pwc_wakeup_pin_enable(PWC_WAKEUP_PIN_1, TRUE);

```

• Revision: None.

#### 1.5.4 Precautions on LDO use

Description:

The LDO output voltage can be adjusted to reduce overall power consumption, but the following two points worth noting:

- 1) Disable PWC clock five LICK clock cycles after LDO configuration by software

- 2) The interval time between two LDO configurations must be greater than 5 LICK clock cycles

- Workaround: Follow the instructions below after adjusting LDO output voltage

```

pwc_ldo_output_voltage_set(PWC_LDO_OUTPUT_1V0);

crm_sysclk_switch_status_get();///<access SBUS

for ( delay_index = 0; delay_index < 80; delay_index++) ///< 5 LICK clock delay at 8MHz

{

___ISB();

}

/* Disable PWC clock, enter sleep mode, enter deepsleep mode, start another LDO configuration */

```

Revision: None.

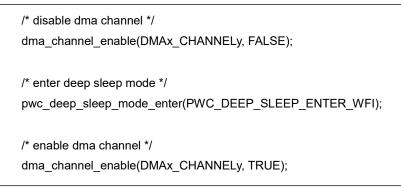

# 1.5.5 Entering Deepsleep mode during DMA/EDMA transfer causes data transfer error

Description:

Executing Deepsleep command during DMA/EDMA transfer likely causes DMA/EDMA to transfer wrong data after waking up from Deepsleeep mode.

Workaround:

Disable DMA/EDMA prior to Deepsleep mode entry, and then enable it after waking up from Deepsleeep mode. See below:

Revision:

None.

### 1.6 SDRAM

### 1.6.1 SDRAM read error in burst read mode

• Description:

When BSTR (burst read) bit of the SDRAM controller is enabled, SDRAM read error may occur.

• Workaround:

Do not use BSTP (Burst Read) feature in SDRAM.

• Revision:

Revision B has fixed this issue.

#### 1.6.2 SDRAM low-power mode limitations

• Description:

When SDRAM is configured in self-refresh or power-down mode, read/write access to SDRAM device in the process of SDRAM entering low-power mode may not be executed.

• Workaround:

Do not read/write from/to SDRAM when the self-refresh or power-down mode is being entered.

After self-refresh or power-down command is sent, it is necessary to ensure that the SDRAM status has switched successfully to self-refresh/power-down mode (get SDRAM status by reading SDRAM\_STS register), and wait until the BUSY bit becomes 0 before performing read/write access to SDRAM.

• Revision:

None.

### **1.6.3 SDRAM and other XMC static memory usage limitations**

• Description:

It is not allowed to access SRAM and other XMC static memories simultaneously.

• Workaround:

If there is a need to use SDRAM and other XMC static memories simultaneously, PSRAM or SRAM is recommended.

Revision:

For Revision B, SDRAM, XMC PSRAM, NOR FLASH and SRAM can be used at the same time but it should be noted that SDRAM must be initialized before use and SDRAM can not be set in Low-power mode. But except this, other XMC static memories such as NAND and PC card cannot be used simultaneously.

## 1.7 SPI

### 1.7.1 CS pulse flag is set in SPI slave TI mode

• Description:

In SPI slave TI mode, if CS and SCK pin are disturbed when SPI is not enabled, a frame format error would occur and an error interrupt is generated.

• Workaround:

Enable or disable TI mode and SPI simultaneously.

• Revision:

None.

# 1.7.2 CS failing edge not synchronized in SPI slave hardware CS mode

• Description:

In SPI slave hardware CS mode (non TI mode), the initial CLK synchronization for data transfer is not performed at each CS falling edge.

• Workaround:

Solution A: Strictly control the slave CS line, pull high the CS line as soon as the communication is complete.

Solution B: Enable CRC check. Once a CRC error is detected, reset SPI and restart handshake communication.

Revision:

None.

# 1.7.3 Unable to clear data reception DMA transfer request by reading DT register

• Description:

For example, for those applications which use SPI full-duplex function for time-sharing receive and transmit, the invalid data reception DMA transfer request, which is set during SPI transmission, cannot be cleared by reading DT register.

Workaround:

When SPI reception DMA channel is turned off, you can clear DMA request by disabling SPI (not reading DT register), and then enabling SPI at a place where you want to start communication.

Revision: None.

### 1.8 **QSPI**

### 1.8.1 QSPI access error when QSPI is not initialized as an XIP port

• Description:

If the QSPI is not initialized as an XIP port, reading QSPI address through memory read or debug mode will get program error.

• Workaround:

Do not read QSPI addresses when the QSPI is not yet be initialized as an XIP port.

• Revision:

Revision B has fixed this issue.

### 1.8.2 Counter error in QSPI XIP port D mode write configuration

• Description 1:

When the following two conditions are present during the use of QSPI, it is likely that the XIPW\_DCNT becomes invalid, acting like XIPW\_DCNT=1, so that the efficiency of QSPI write operation will be reduced compared with its expected values.

The two conditions are as follows:

- 1. QSPI is initialized as an XIP endpoint

- 2. Select mode D when it comes to write mode configuration

- Workaround:

Try to use mode T as much as possible. If there is a need to use mode D, it is necessary to evaluate its impact on write operation.

Revision:

Revision B has fixed this issue.

#### 1.8.3 **QSPI** Cache usage limitations

Description:

QSPI Cache is an enhanced edition of XIP port. This feature is enabled or disabled through the BYPASSC bit of the XIP CMD\_W3 register. (It is enabled by default. BYPASSC=1 disables it)

Such feature, however, has its prerequisites for use: it can be used only when the following scenarios are all present, otherwise, an error may occur.

• Workaround:

Enable this feature only when both of the following conditions are met.

- 1 XIP Read only (extend external Flash)

- 2 XIP T mode (XIPR\_SEL bit is set to 1)

- Revision:

Revision B has fixed this issue.

#### 1.8.4 QSPI clock polary selection limitation

Description:

When the division value of CLKDIV is 2/4/6/8, it is possible to select mode 0 or mode 3 using the SCKMODE bit.

When the division value of CLKDIV is 3/5/10/12, SCKMODE bit configuration is invalid and the actual SCK output is mode 0.

• Workaround:

If there is a need to use mode 3, the CLKDIV division value should be 2/4/6/8.

Revision

Revision B has fixed this issue.

#### **1.8.5 DMA P2M mode usage condition in QSPI command port mode**

Description:

When QSPI is configured in command port mode, a specific condition must be met for data transfer using DMA P2M mode, detailed as follows.

Workaround:

When QSPI is configured in command port mode, to use DMA P2M mode to transfer data, the MSIZE must select word format, and data size must be a multiple of 4.

Revision:

None.

# 1.8.6 Excess dummy clock sent after read operation in QSPI command port mode

• Description:

When QSPI is configured in command port mode, after the completion of read access, an additional dummy clock will be sent, which has no impact on applications in most cases.

• Workaround:

None.

Revision:

None.

### 1.9 USART

### 1.9.1 USART ROERR flag is set exceptionally

• Description:

As a receiver, if the RX line low level is detected and a Start bit is detected accordingly during STOP bit, the ROERR flag will be set exceptionally. This causes a higher baud rate of the tramsmitter and ROERR flag to be set when sending consecutive data.

Workaround:

Do not use ROERR flag to determine whether data reception overruns or not. The USART must not enable error interrupt ERRIEN during DMA reception.

Revision

Revision B has fixed this issue.

### 1.10 ADVTM

### 1.10.1 How to clear TMR-triggered DAM requests

• Description:

TMR-induced DMA request cannot be cleared by resetting/setting the corresponding DMA request enable bit in the TMRx\_IDEN register.

Workaround:

Before enabling DMA channel, reset TMR (reset CRM clock of TMR) and initialize TMR to clear pending DMA requests.

Revision

Revision B has fixed this issue.

#### 1.10.2 TMR overrun in encoder mode counter

#### • Description:

In encoder counting mode, if the counter counts back and forth between 0 and PR, the OVFIF is not set at an overrun or underrun event.

• Method 1:

Configure the C3IF and C4IF channels of the TMR (where an encoder is being used) as output mode, C3DT = AR, C4DT = 0, and enable C3IF and C4IF interrupts.

C3IF event & downcounting indicates an underrun;

C4IF event & upcounting indicates an overrun;

This method has its limitation: If the input frequency of the encoder mode counter were too fast, interrupts would occur frequently and need to be handled by software, causing not enough time for software to deal with interrupts. Thus this method applies to the scenario where the external input frequency of the encoder is not so fast.

• Method 2:

Turn to a TMR with enhanced mode (the counter can be extended from 16-bit to 32-bit width) in order to expand the encoder's counting range that detects forward and reverse rotation, and configure the initial value of the counter to PR/2 so as to prevent the timer from overflowing. This method has its limitation: The forward and reverse rotation of the encoder must be limited to a certain range. An overflow still occurs if the encoder were always rotated in one direction. This method applies to the scenario where the rotation of the encoder is controlled at a certain range.

Revision

None.

### 1.10.3 Break input failed when TMREN=0

Description:

When TMREN=0 (timer is disabled), break input is inactive, causint it unable to trigger break event or interrupt.

As an example, in one-pulse mode, the TMREN is automatically cleared at the end of onecycle counting. In such case, due to the break input being disabled, the output enable bit (OEN) cannot be cleared, nor is the break flag bit set.

• Workaround:

None.

Revision:

None.

## 1.11 ERTC

## **1.11.1 Writing ERTC occupies APB for 4 ERTC clock cyles**

• Description:

Writing ERTC register takes approximately four ERTC CLK clock cycles to be synchronized with the battery powered domain, causing APB1 to be occupied and DMA transfer on APB1 to be halted during this period until the completion of the operation process.

• Workaround:

After ERTC initialization, if ERTC features can satisfy users' needs, try to reduce the times of writing ERTC registers so as to reduce its impact on system.

• Revision:

None.

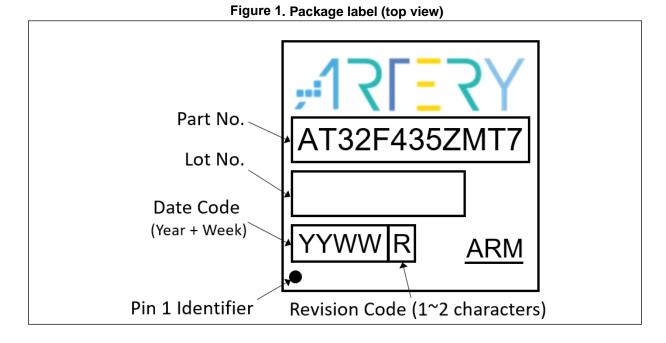

## 2 Revision code on device marking

Figure 1 shows the location of revision code on AT32F435/437 device marking. The first code is R (revision code). For example, if B is shown in the R location, it means that the hardware revision of this device is silicon B.

## **3** Document revision history

| Table 4 | . Document | revision | history |

|---------|------------|----------|---------|

|---------|------------|----------|---------|

| Date       | Revision | Changes                                                                             |  |  |

|------------|----------|-------------------------------------------------------------------------------------|--|--|

| 2021.9.30  | 2.0.0    | Initial release                                                                     |  |  |

| 2022.3.1   |          | 1. Added SDRAM low-power mode limitations.                                          |  |  |

|            | 2.0.1    | 2. Added SDRAM and other XMC static memory usage limitations.                       |  |  |

|            | 2.0.1    | 3. Added Counter error in QSPI XIP port D mode write configuration                  |  |  |

|            |          | 4. Added Failed to filter RTR bit of standard frame in 32-bit identifier mask mode. |  |  |

| 2022.3.30  | 2.0.2    | 1. Added SWEF flag is set when enabling a standby-mode wakeup pin.                  |  |  |

| 2022.3.30  | 2.0.2    | 2. Added QSPI Cache .                                                               |  |  |

|            |          | 1. Added CAN sends unexpected messages in case of narrow pulse disturbance          |  |  |

|            |          | on BS2.                                                                             |  |  |

|            |          | 2. Added QSPI Cache .                                                               |  |  |

| 0000 04 45 |          | 3. Added First data error in I2S PCM standard long frame receive-only mode.         |  |  |

| 2022.04.15 | 2.0.3    | 4. Added UDR flag is set in I2S slave transmission mode and discontinuous           |  |  |

|            |          | communication state.                                                                |  |  |

|            |          | 5. Added Data reception error when I2S 24-bit data is packed into 32-bit format.    |  |  |

|            |          | 6. Added 1.7.2 CS failing edge not synchronized in SPI slave hardware CS mode       |  |  |

|            |          | 1. Modified the description of the section 1.8.3 QSPI Cache usage limitation        |  |  |

|            | 2.0.4    | 2. Added an example case in the 1.1.2 Failed to filter RTR bit of standard frame in |  |  |

| 2022.04.27 |          | 32-bit identifier mask mode                                                         |  |  |

|            |          | 3. Added an example case in the 1.5.3 SWEF flag is set when enabling a              |  |  |

|            |          | standby-mode wakeup pin                                                             |  |  |

| 2022.08.15 | 2.0.5    | Updated 1.8.3 QSPI Cache usage limitation                                           |  |  |

| 2022.08.23 | 2.0.6    | Added 1.6.3 SDRAM and other XMC static memory usage limitations                     |  |  |

|            |          | Added 1.11.1 Writing ERTC occupies APB for 4 ERTC clock cyles                       |  |  |

| 2022.10.19 | 2.0.7    | Added 1.5.4 Precautions on LDO use                                                  |  |  |

|            |          | Added 1.8.5 QSPI clock polary selection limitation                                  |  |  |

| 2023.03.09 | 2.0.8    | Added Table 1 Device identification                                                 |  |  |

|            |          | 1. Added 1.10.3 Break input failed when TMREN=0                                     |  |  |

|            | 2.0.9    | 2. Updated the descriptions of 1.1.1 Bit stuffing error causes the next data out-   |  |  |

|            |          | of-order during CAN communication                                                   |  |  |

| 2023.08.03 |          | 3. Added 1.1.4 Fail to cancel mailbox transmit command when CAN bus                 |  |  |

|            |          | disconnected                                                                        |  |  |

|            |          | 4. Added 1.8.5 DMA P2M mode usage condition in QSPI command port mode               |  |  |

|            |          | 5. Added 1.8.6 Excess dummy clock sent after read operation in QSPI                 |  |  |

|            |          | command port mode                                                                   |  |  |

| 2023.08.17 | 2.0.10   | 6. Updated the descriptions of 1.8.3 QSPI Cache usage limitations                   |  |  |

#### **IMPORTANT NOTICE – PLEASE READ CAREFULLY**

Purchasers are solely responsible for the selection and use of ARTERY's products and services, and ARTERY assumes no liability whatsoever relating to the choice, selection or use of the ARTERY products and services described herein

No license, express or implied, to any intellectual property rights is granted under this document. If any part of this document deals with any third party products or services, it shall not be deemed a license granted by ARTERY for the use of such third party products or services, or any intellectual property contained therein, or considered as a warranty regarding the use in any manner of such third party products or services or any intellectual property contained therein.

Unless otherwise specified in ARTERY's terms and conditions of sale, ARTERY provides no warranties, express or implied, regarding the use and/or sale of ARTERY products, including but not limited to any implied warranties of merchantability, fitness for a particular purpose (and their equivalents under the laws of any jurisdiction), or infringement on any patent, copyright or other intellectual property right.

Purchasers hereby agree that ARTERY's products are not designed or authorized for use in: (A) any application with special requirements of safety such as life support and active implantable device, or system with functional safety requirements; (B) any aircraft application; (C) any aerospace application or environment; (D) any weapon application, and/or (E) or other uses where the failure of the device or product could result in personal injury, death, property damage. Purchasers' unauthorized use of them in the aforementioned applications, even if with a written notice, is solely at purchasers' risk, and Purchasers are solely responsible for meeting all legal and regulatory requirements in such use.

Resale of ARTERY products with provisions different from the statements and/or technical characteristics stated in this document shall immediately void any warranty grant by ARTERY for ARTERY's products or services described herein and shall not create or expand any liability of ARTERY in any manner whatsoever.

© 2023 Artery Technology -All rights reserved