# ARM<sup>®</sup>-based 32-bit Cortex<sup>®</sup>-M0+ MCU with 16 to 64 KB Flash, sLib, 10 timers, ADC, 10 communication interfaces (1 CAN)

#### ■ Core: ARM<sup>®</sup> 32-bit Cortex<sup>®</sup>-M0+ CPU

- 80 MHz maximum frequency, with a Memory Protection Unit (MPU), single-cycle multiplication

- Memories

- 16 to 64 Kbytes of Flash memory

- 4 Kbytes of boot memory used as a Bootloader or as a general instruction/data memory (one-timeconfigured)

- sLib: configurable part of main Flash set as a library area with code executable but secured, nonreadable

- 9 Kbytes of SRAM (8 Kbytes with parity check)

#### Power control (PWC)

- 1.71 ~ 3.6 V power supply

- Power-on reset (POR), low voltage reset (LVR), power voltage monitor (PVM)

- Low power modes: Sleep, Deepsleep and Standby modes; 5 WKUP pins for wakeup from Standby mode

- 5 x 32-bit battery powered registers (BPR)

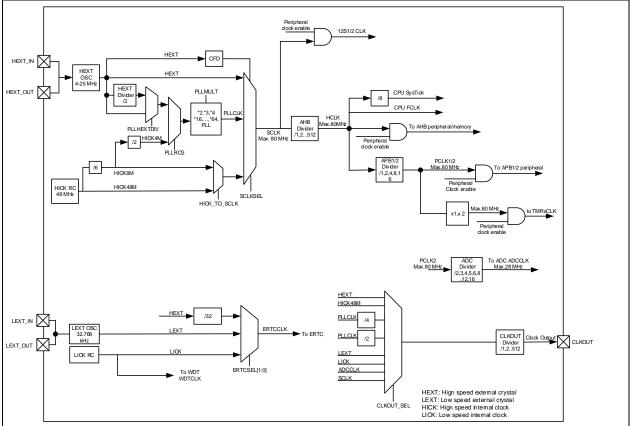

#### Clock, reset and power management

- 4 to 25 MHz crystal oscillator (HEXT)

- Internal 48 MHz factory-trimmed HICK

- 32 kHz crystal (LEXT)

- Low-speed internal clock (LICK)

- Analog

- 1 x 12-bit 2 MSPS A/D converter, up to 15 external input channels, 12-bit/10-bit/8-bit/6-bit configurable resolution, hardware oversampling up to equivalent 16-bit resolution

- Internal reference voltage (VINTRV)

- Up to 39 fast GPIOs

- Core dedicated single-cycle GPIO bus

- All mappable on external interrupts

- Almost all 5 V-tolerant

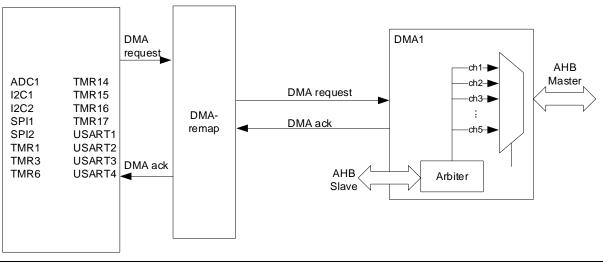

- DMA

- 1 x 5-channel DMA controller

- Up to 10 timers

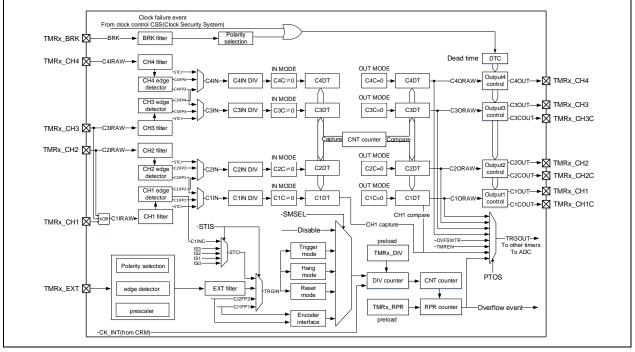

- 1 x 16-bit 7-channel advanced timer, including 3 pairs of complementary channels for PWM output, with dead-time generator and emergency brake

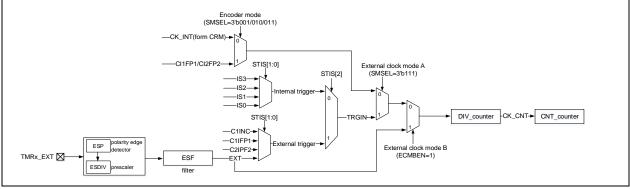

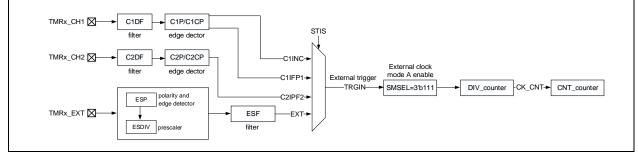

- Up to 5 x 16-bit general-purpose timers, each with 4 IC/OC/PWM or pulse counter and quadrature (incremental) encoder input

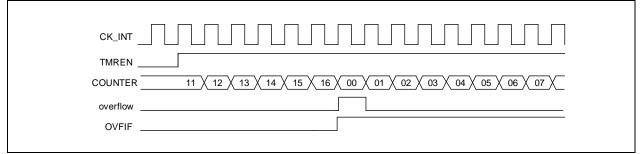

- 1 x 16-bit basic timer

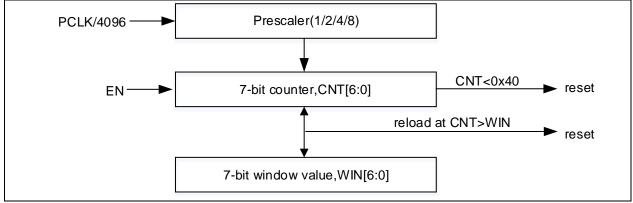

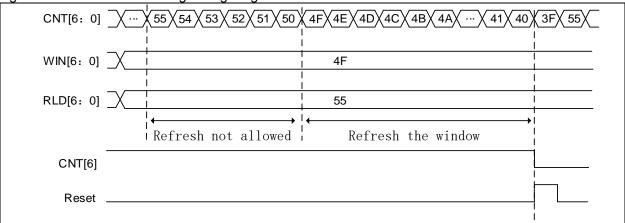

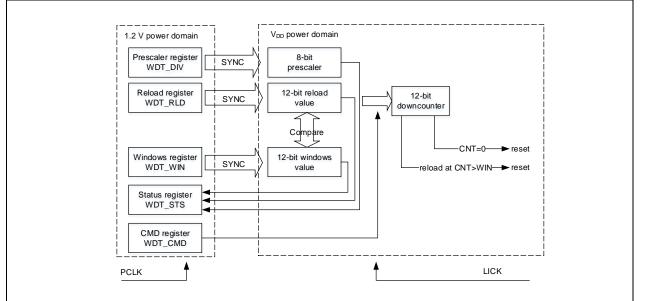

- 2 x watchdog timers (general WDT and windowed WWDT)

- SysTick timer: a 24-bit downcounter

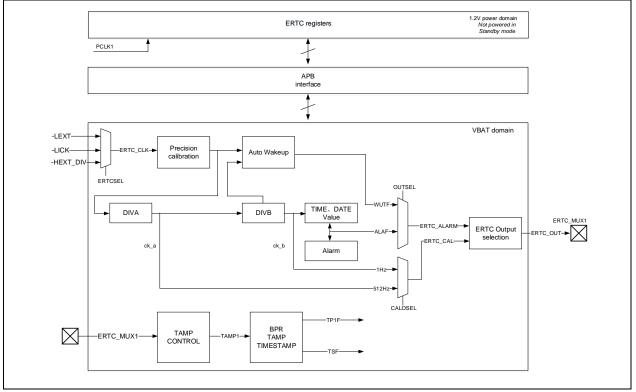

- ERTC: enhanced RTC, with alarm, subsecond precision, hardware calendar, and calibration

- Up to 10 communication interfaces

- 2 x I<sup>2</sup>C interfaces (SMBus/PMBus) supporting fast mode plus (1 MHz), with wakeup from Deepsleep mode

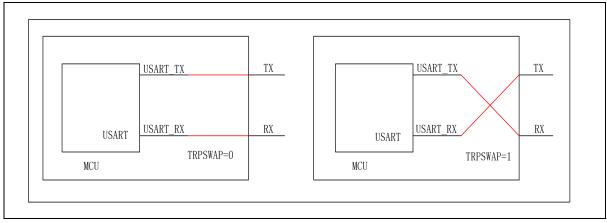

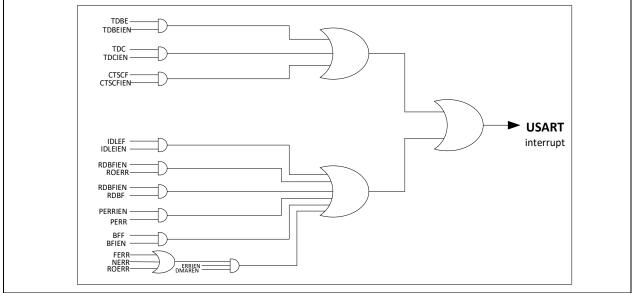

- 4 x USARTs, supporting synchronous SPI and modem control; with ISO7816 interface, LIN, IrDA and RS485 driver enable, TX/RX swap

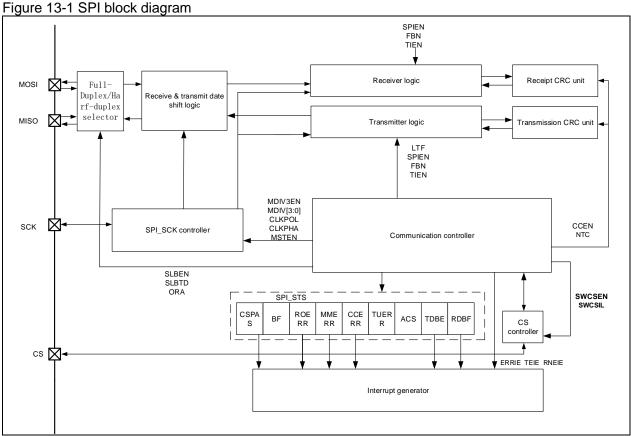

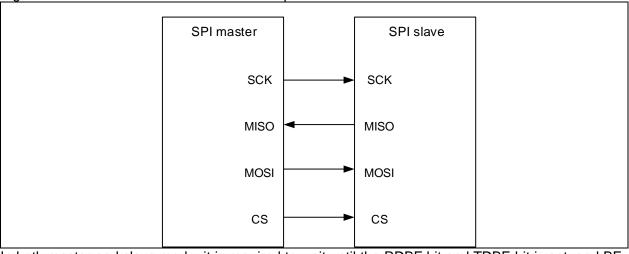

- 2 x SPIs (36 MHz), all with multiplexed half-duplex  $I^2S;$

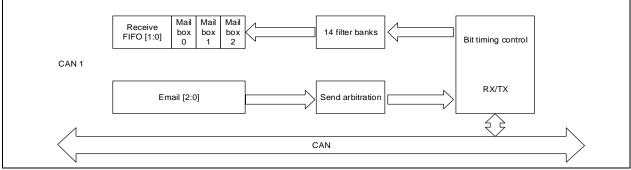

- CAN interface (2.0B Active), with 256 bytes of dedicated buffer

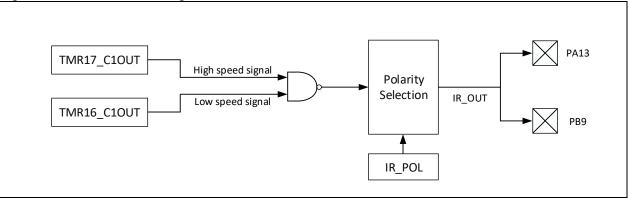

- Infrared transmitter (IRTMR)

- 96-bit ID (UID)

- Debug mode

- Serial wire debug (SWD) and serial wire output (SWO)

- Temperature range: -40 to +105 °C

- Packaging

- LQFP48 7 x 7 mm

- LQFP32 7 x 7 mm

- QFN32 5 x 5 mm

- QFN32 4 x 4 mm

- QFN28 4 x 4 mm

- QFN20 3 x 3 mm

- TSSOP20 6.5 x 4.4 mm

- List of Models

| Internal Flash | Model          |

|----------------|----------------|

|                | AT32L021C8T7,  |

|                | AT32L021K8T7,  |

|                | AT32L021K8U7,  |

| 64 KB          | AT32L021K8U7-4 |

|                | AT32L021F8P7,  |

|                | AT32L021F8U7,  |

|                | AT32L021G8U7   |

|                | AT32L021C6T7,  |

|                | AT32L021K6T7,  |

|                | AT32L021K6U7,  |

| 32 KB          | AT32L021K6U7-4 |

|                | AT32L021F6P7,  |

|                | AT32L021F6U7,  |

|                | AT32L021G6U7   |

|                | AT32L021C4T7,  |

|                | AT32L021K4T7,  |

|                | AT32L021K4U7,  |

| 16 KB          | AT32L021K4U7-4 |

|                | AT32L021F4P7,  |

|                | AT32L021F4U7,  |

|                | AT32L021G4U7   |

#### Contents

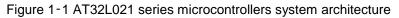

| 1 | Syste                                                                                                 | em architecture24                                                                                                                                                                                                                                                                                                                                                                                                               | ŀ                |

|---|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

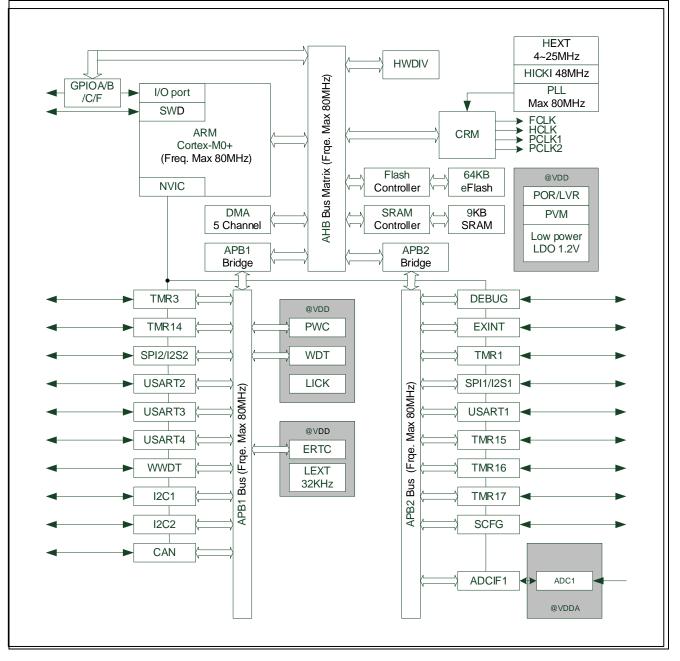

|   | 1.1                                                                                                   | System overview25                                                                                                                                                                                                                                                                                                                                                                                                               | 5                |

|   |                                                                                                       | 1.1.1 ARM <sup>®</sup> Cortex <sup>®</sup> -M0+ processor 25                                                                                                                                                                                                                                                                                                                                                                    | 5                |

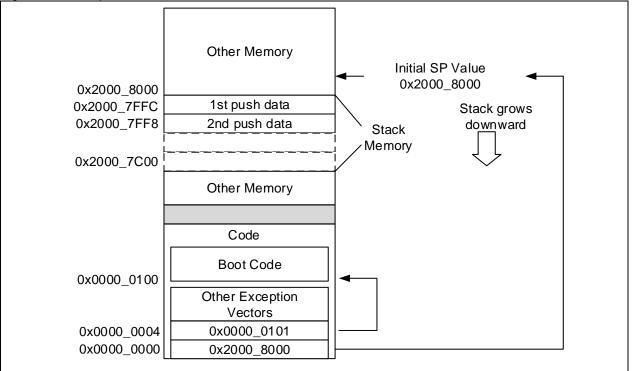

|   |                                                                                                       | 1.1.2 Interrupt and exception vectors 25                                                                                                                                                                                                                                                                                                                                                                                        | 5                |

|   |                                                                                                       | 1.1.3 System Tick (SysTick) 26                                                                                                                                                                                                                                                                                                                                                                                                  | 5                |

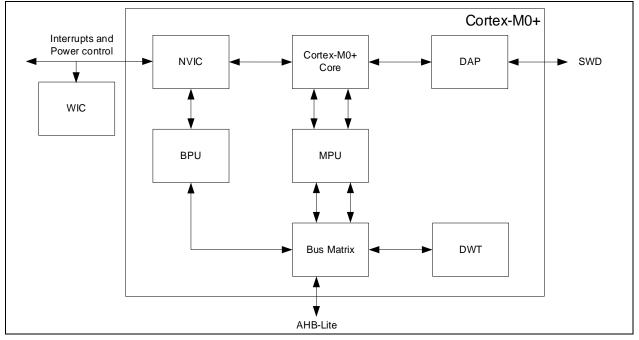

|   |                                                                                                       | 1.1.4 Reset                                                                                                                                                                                                                                                                                                                                                                                                                     | 5                |

|   | 1.2                                                                                                   | List of abbreviations for registers27                                                                                                                                                                                                                                                                                                                                                                                           | 7                |

|   | 1.3                                                                                                   | Device characteristics information                                                                                                                                                                                                                                                                                                                                                                                              | 3                |

|   |                                                                                                       | 1.3.1 Flash memory size register 28                                                                                                                                                                                                                                                                                                                                                                                             | 3                |

|   |                                                                                                       | 1.3.2 Device electronic signature                                                                                                                                                                                                                                                                                                                                                                                               | 3                |

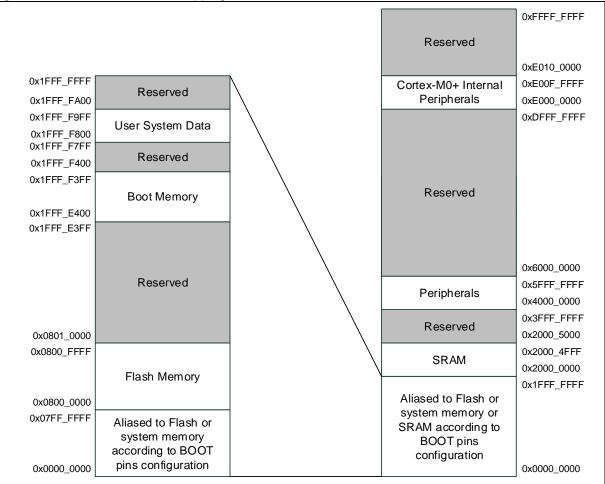

| 2 | Mem                                                                                                   | ory resources                                                                                                                                                                                                                                                                                                                                                                                                                   | )                |

|   | 2.1                                                                                                   | Internal memory address map29                                                                                                                                                                                                                                                                                                                                                                                                   | )                |

|   | 2.2                                                                                                   | Flash memory29                                                                                                                                                                                                                                                                                                                                                                                                                  | )                |

|   | 2.3                                                                                                   | SRAM memory                                                                                                                                                                                                                                                                                                                                                                                                                     | )                |

|   | 2.4                                                                                                   | Peripheral address map                                                                                                                                                                                                                                                                                                                                                                                                          | )                |

|   |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  |

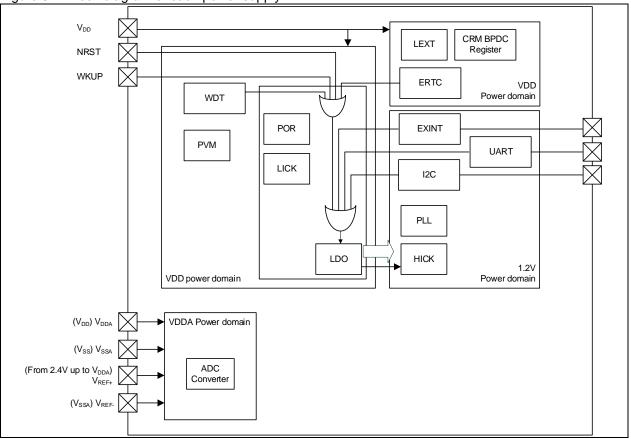

| 3 | Powe                                                                                                  | er control (PWC)                                                                                                                                                                                                                                                                                                                                                                                                                | 3                |

| 3 | <b>Powe</b><br>3.1                                                                                    | er control (PWC)                                                                                                                                                                                                                                                                                                                                                                                                                |                  |

| 3 |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3                |

| 3 | 3.1                                                                                                   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                    | 3                |

| 3 | 3.1<br>3.2                                                                                            | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                    | 3                |

| 3 | 3.1<br>3.2<br>3.3                                                                                     | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                    | 3<br>3<br>3      |

| 3 | 3.1<br>3.2<br>3.3<br>3.4                                                                              | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                    | 3<br>3<br>4<br>5 |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5                                                                       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                    | 3<br>3<br>4<br>5 |

| 3 | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> </ul>              | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                    | 3 3 4 5 5 6      |

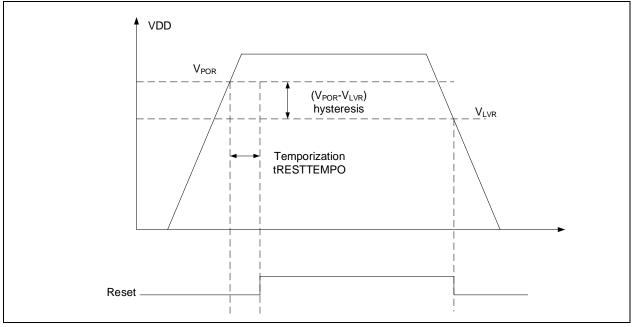

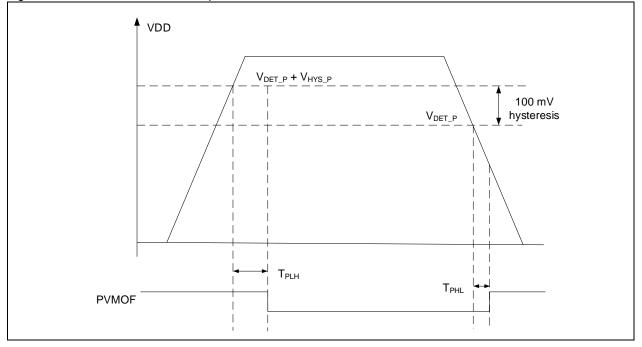

| 3 | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> </ul>              | Introduction       33         Main features       33         POR/LVR       33         Power voltage monitor (PVM)       34         Power domain       35         Power-saving modes       35         PWC registers       36                                                                                                                                                                                                     | 3 3 4 5 5 6      |

| 3 | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> </ul> | Introduction       33         Main features       33         POR/LVR       33         Power voltage monitor (PVM)       34         Power domain       35         Power-saving modes       35         PWC registers       36         3.7.1 Power control register (PWC_CTRL)       36                                                                                                                                            | 3345567          |

|   | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> </ul> | Introduction33Main features33POR/LVR33Power voltage monitor (PVM)34Power domain35Power-saving modes35PWC registers363.7.1 Power control register (PWC_CTRL)363.7.2 Power control/status register (PWC_CTRLSTS)37                                                                                                                                                                                                                |                  |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br><b>Cloc</b>                                          | Introduction       33         Main features       33         POR/LVR       33         Power voltage monitor (PVM)       34         Power domain       35         Power domain       35         Power-saving modes       35         PWC registers       36         3.7.1 Power control register (PWC_CTRL)       36         3.7.2 Power control/status register (PWC_CTRLSTS)       37         k and reset manage (CRM)       39 | 33455679         |

# 475<u>-</u>751÷

|       | 4.1.3 Peripheral clock                                    | 40 |

|-------|-----------------------------------------------------------|----|

|       | 4.1.4 Clock fail detector                                 | 40 |

|       | 4.1.5 Clock output                                        | 41 |

|       | 4.1.6 Interrupts                                          | 41 |

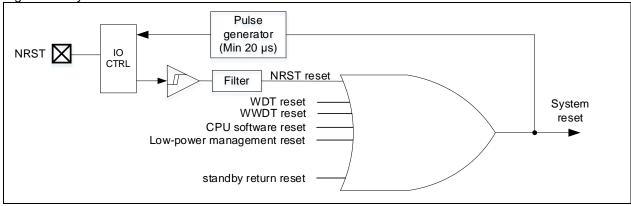

| 4.2   | Reset                                                     | 41 |

|       | 4.2.1 System reset                                        | 41 |

|       | 4.2.2 Battery powered domain reset                        | 41 |

| 4.3   | CRM registers                                             | 42 |

|       | 4.3.1 Clock control register (CRM_CTRL)                   | 42 |

|       | 4.3.2 Clock configuration register (CRM_CFG)              | 43 |

|       | 4.3.3 Clock interrupt register (CRM_CLKINT)               | 45 |

|       | 4.3.4 APB2 peripheral reset register (CRM_APB2RST)        | 46 |

|       | 4.3.5 APB1 peripheral reset register (CRM_APB1RST)        | 46 |

|       | 4.3.6 AHB peripheral clock enable register (CRM_AHBEN)    | 47 |

|       | 4.3.7 APB2 peripheral clock enable register (CRM_APB2EN)  | 48 |

|       | 4.3.8 APB1 peripheral clock enable register (CRM_APB1EN)  | 48 |

|       | 4.3.9 Battery powered domain control register (CRM_BPDC)  | 49 |

|       | 4.3.10 Control/status register (CRM_CTRLSTS)              | 50 |

|       | 4.3.11 AHB peripheral reset register (CRM_AHBRST)         | 51 |

|       | 4.3.12 PLL configuration register (CRM_PLL)               | 51 |

|       | 4.3.13 Additional register 1 (CRM_MISC1)                  | 52 |

|       | 4.3.14 HSE driving strength control register (CRM_HSEDRV) | 52 |

|       | 4.3.15 Peripheral independent clock select (CRM_PICLKS)   | 52 |

|       | 4.3.16 Additional register 2 (CRM_MISC2)                  | 53 |

| Flash | n memory controller (FLASH)                               | 54 |

| 5.1   | FLASH introduction                                        | 54 |

| 5.2   | Flash memory operation                                    | 56 |

|       | 5.2.1 Unlock/lock                                         | 56 |

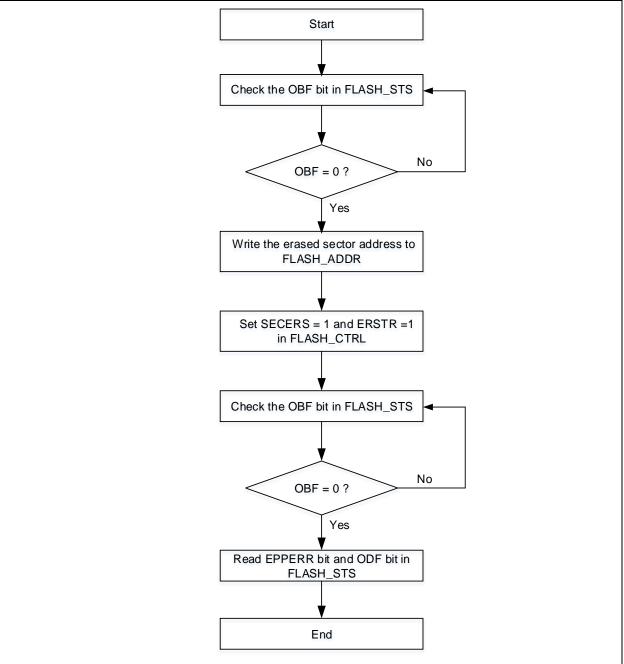

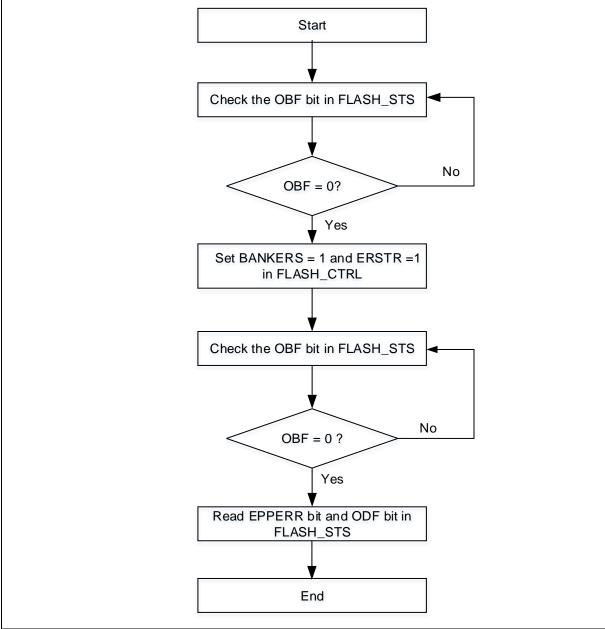

|       | 5.2.2 Erase operation                                     | 56 |

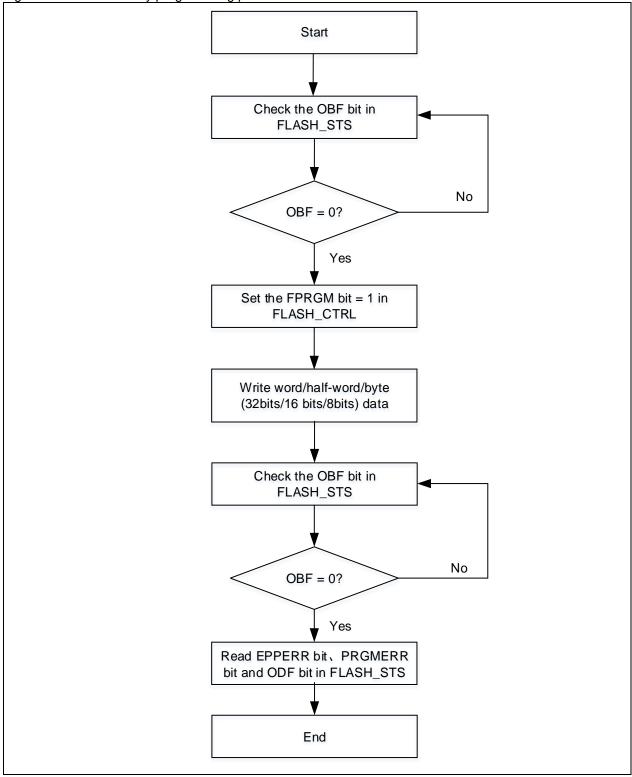

|       | 5.2.3 Programming operation                               | 58 |

|       | 5.2.4 Read operation                                      | 59 |

| 5.3   | Main Flash memory extension area                          | 59 |

| 5.4   | User system data area operation                           | 60 |

|       |                                                           |    |

5

# Υ<mark>ΣΞ</mark>ΊΣΓμ

|     | 5.4.1 Unlock/lock                                                                   |

|-----|-------------------------------------------------------------------------------------|

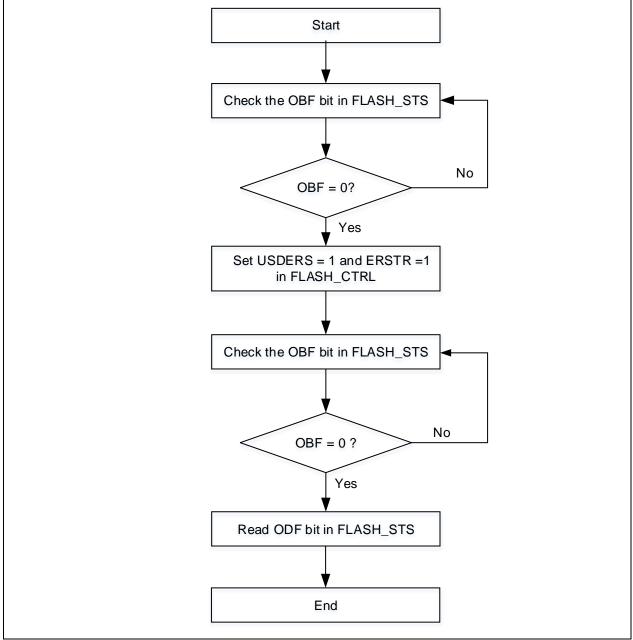

|     | 5.4.2 Erase operation 60                                                            |

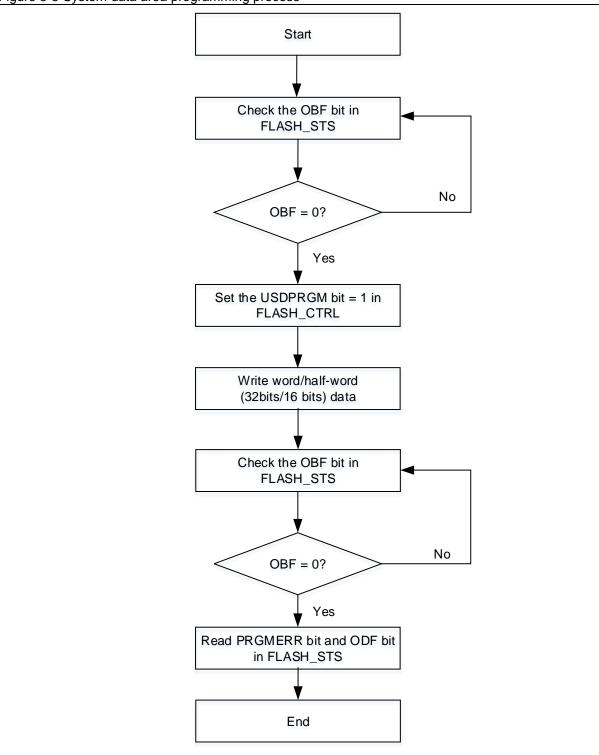

|     | 5.4.3 Programming operation 61                                                      |

|     | 5.4.4 Read operation 62                                                             |

| 5.5 | Flash memory protection62                                                           |

|     | 5.5.1 Access protection                                                             |

|     | 5.5.2 Erase/program protection                                                      |

| 5.6 | Read performance63                                                                  |

| 5.7 | Special functions64                                                                 |

|     | 5.7.1 Security library settings 64                                                  |

|     | 5.7.2 Boot memory used as Flash memory extension                                    |

|     | 5.7.3 CRC verify 65                                                                 |

| 5.8 | Flash memory registers65                                                            |

|     | 5.8.1 Flash performance select register (FLASH_PSR)                                 |

|     | 5.8.2 Flash unlock register (FLASH_UNLOCK)                                          |

|     | 5.8.3 Flash user system data unlock register (FLASH_USD_UNLOCK) 67                  |

|     | 5.8.4 Flash status register (FLASH_STS) 67                                          |

|     | 5.8.5 Flash control register (FLASH_CTRL)                                           |

|     | 5.8.6 Flash address register (FLASH_ADDR)68                                         |

|     | 5.8.7 User system data register (FLASH_USD)                                         |

|     | 5.8.8 Erase/program protection status register (FLASH_EPPS) 68                      |

|     | 5.8.9 Flash security library status register 0 (SLIB_STS0)68                        |

|     | 5.8.10 Flash security library status register 1 (SLIB_STS1)69                       |

|     | 5.8.11 Flash security library password clear register (SLIB_PWD_CLR) 69             |

|     | 5.8.12 Security library additional status register (SLIB_MISC_STS)                  |

|     | 5.8.13 Flash CRC address register (FLASH_CRC_ADDR)                                  |

|     | 5.8.14 Flash CRC control register (FLASH_CRC_CTRL)                                  |

|     | 5.8.15 Flash CRC check result register (FLASH_CRC_CHKR)                             |

|     | 5.8.16 Security library password setting register (SLIB_SET_PWD)                    |

|     | 5.8.17 Security library address setting register (SLIB_SET_RANGE) 71                |

|     | 5.8.18 Flash extension memory security library setting register (EM_SLIB_SET)<br>71 |

|     | 5.8.19 Boot memory mode setting register (BTM_MODE_SET) 72                          |

|     | 5.8.20 Security library unlock register (SLIB_UNLOCK)                               |

# <u>, 12L55</u>

| <ul> <li>6.2 Function overview</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | GPIO   | s and IOMUX7                                                           | 3          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------------------------------------------------|------------|

| <ul> <li>6.2.1 GPIO structure.</li> <li>6.2.2 GPIO reset status.</li> <li>6.2.3 General-purpose input configuration</li> <li>6.2.4 Analog input/output configuration</li> <li>6.2.5 General-purpose output configuration</li> <li>6.2.6 GPIO port protection</li> <li>6.2.7 IOMUX structure</li> <li>6.2.8 Multiplexed function pull-up/pull-down configuration</li> <li>6.2.9 IOMUX input/output</li> <li>6.2.10 Peripheral multiplexed function configuration</li> <li>6.2.11 IOMUX mapping priority.</li> <li>6.2.12 External interrupt/wake-up lines</li> <li>6.3 GPIO registers.</li> <li>6.3.1 GPIO configuration register (GPIOx_CFGR) (x=AC,F)</li> <li>6.3.2 GPIO output mode register (GPIOx_OMODE) (x=AC,F)</li> <li>6.3.3 GPIO drive capability register (GPIOx_ODRVR) (x=AC,F)</li> <li>6.3.4 GPIO pull-up/pull-down register (GPIOx_ODT) (x=AC,F)</li> <li>6.3.5 GPIO input data register (GPIOx_CCR) (x=AC,F)</li> <li>6.3.6 GPIO output data register (GPIOx_SCR) (x=AC,F)</li> <li>6.3.7 GPIO set/clear register (GPIOx_SCR) (x=AC,F)</li> <li>6.3.8 GPIO write protection register (GPIOx_WPR) (x=AC,F)</li> <li>6.3.9 GPIO multiplexed function low register (GPIOx_MUXL) (x=AC,F)</li> <li>6.3.10 GPIO multiplexed function low register (GPIOx_MUXL) (x=AC,F)</li> <li>6.3.13 GPIO port bit clear register (GPIOx_TCGR) (x=AC,F)</li> <li>6.3.13 GPIO port bit clear register (GPIOx_TCGR) (x=AC,F)</li> <li>6.3.13 GPIO port bit clear register (GPIOx_TCGR) (x=AC,F)</li> <li>6.3.13 GPIO huge current control register (GPIOx_HDRV) (x=AC,F)</li> <li>6.3.13 GPIO huge current control register (GPIOx_HDRV) (x=AC,F)</li> </ul> | 6.1    | Introduction                                                           | '3         |

| <ul> <li>6.2.2 GPIO reset status</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6.2    | Function overview7                                                     | '3         |

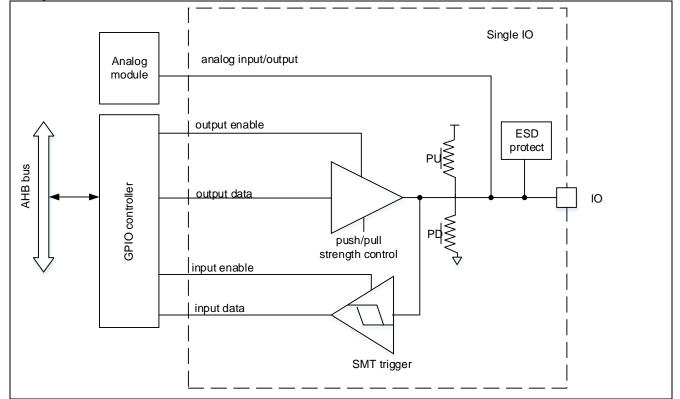

| <ul> <li>6.2.3 General-purpose input configuration.</li> <li>6.2.4 Analog input/output configuration</li> <li>6.2.5 General-purpose output configuration</li> <li>6.2.6 GPIO port protection</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        | 6.2.1 GPIO structure                                                   | 73         |

| <ul> <li>6.2.4 Analog input/output configuration</li> <li>6.2.5 General-purpose output configuration</li> <li>6.2.6 GPIO port protection</li> <li>6.2.7 IOMUX structure</li> <li>6.2.8 Multiplexed function pull-up/pull-down configuration</li> <li>6.2.9 IOMUX input/output</li> <li>6.2.10 Peripheral multiplexed function configuration</li> <li>6.2.11 IOMUX mapping priority</li> <li>6.2.12 External interrupt/wake-up lines</li> <li>6.3 GPIO registers</li> <li>6.3.1 GPIO configuration register (GPIOx_CFGR) (x=AC,F)</li> <li>6.3.2 GPIO output mode register (GPIOx_OMODE) (x=AC,F)</li> <li>6.3.3 GPIO drive capability register (GPIOx_ODRVR) (x=AC,F)</li> <li>6.3.4 GPIO pull-up/pull-down register (GPIOx_PULL) (x=AC,F)</li> <li>6.3.5 GPIO input data register (GPIOx_IDT) (x=AC,F)</li> <li>6.3.6 GPIO output data register (GPIOx_ODT) (x=AC,F)</li> <li>6.3.7 GPIO set/clear register (GPIOx_SCR) (x=AC,F)</li> <li>6.3.8 GPIO write protection register (GPIOx_WPR) (x=AC,F)</li> <li>6.3.9 GPIO multiplexed function low register (GPIOx_MUXL) (x=AC,F)</li> <li>6.3.10 GPIO multiplexed function high register (GPIOx_MUXL) (x=AC,F)</li> <li>6.3.10 GPIO multiplexed function high register (GPIOx_MUXL) (x=AC,F)</li> <li>6.3.12 GPIO port bit clear register (GPIOx_CLR) (x=AC,F)</li> <li>6.3.13 GPIO to to tiggle register (GPIOx_TOGR) (x=AC,F)</li> <li>6.3.13 GPIO port bit toggle register (GPIOx_TDGR) (x=AC,F)</li> <li>6.3.13 GPIO huge current control register (GPIOx_HDRV) (x=AC,F)</li> <li>6.3.13 GPIO huge current control register (GPIOx_HDRV) (x=AC,F)</li> <li>6.3.13 GPIO huge current control register (GPIOx_HDRV) (x=AC,F)</li> </ul>                                                                                                                                                                                                       |        | 6.2.2 GPIO reset status                                                | 74         |

| <ul> <li>6.2.5 General-purpose output configuration.</li> <li>6.2.6 GPIO port protection</li> <li>6.2.7 IOMUX structure</li> <li>6.2.8 Multiplexed function pull-up/pull-down configuration</li> <li>6.2.9 IOMUX input/output</li> <li>6.2.10 Peripheral multiplexed function configuration</li> <li>6.2.11 IOMUX mapping priority.</li> <li>6.2.12 External interrupt/wake-up lines</li> <li>6.3 GPIO registers</li> <li>6.3.1 GPIO configuration register (GPIOx_CFGR) (x=AC,F)</li> <li>6.3.2 GPIO output mode register (GPIOx_OMODE) (x=AC,F)</li> <li>6.3.3 GPIO drive capability register (GPIOx_OMODE) (x=AC,F)</li> <li>6.3.4 GPIO pull-up/pull-down register (GPIOx_PULL) (x=AC,F)</li> <li>6.3.5 GPIO input data register (GPIOX_DDT) (x=AC,F)</li> <li>6.3.6 GPIO output data register (GPIOX_CCF) (x=AC,F)</li> <li>6.3.7 GPIO set/clear register (GPIOX_CCR) (x=AC,F)</li> <li>6.3.8 GPIO write protection register (GPIOX_WPR) (x=AC,F)</li> <li>6.3.9 GPIO multiplexed function low register (GPIOX_MUXL) (x=AC,F)</li> <li>6.3.10 GPIO multiplexed function high register (GPIOX_MUXL) (x=AC,F)</li> <li>6.3.11 GPIO port bit toggle register (GPIOX_CLR) (x=AC,F)</li> <li>6.3.12 GPIO port bit toggle register (GPIOX_TOGR) (x=AC,F)</li> <li>6.3.13 GPIO huge current control register (GPIOX_HDRV) (x=AC,F)</li> <li>6.3.13 GPIO huge current control register (GPIOX_HDRV) (x=AC,F)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | 6.2.3 General-purpose input configuration                              | 74         |

| <ul> <li>6.2.6 GPIO port protection</li> <li>6.2.7 IOMUX structure</li> <li>6.2.8 Multiplexed function pull-up/pull-down configuration</li> <li>6.2.9 IOMUX input/output</li> <li>6.2.10 Peripheral multiplexed function configuration</li> <li>6.2.11 IOMUX mapping priority</li> <li>6.2.12 External interrupt/wake-up lines</li> <li>6.3 GPIO registers</li> <li>6.3.1 GPIO configuration register (GPIOx_CFGR) (x=AC,F)</li> <li>6.3.2 GPIO output mode register (GPIOx_OMODE) (x=AC,F)</li> <li>6.3.3 GPIO drive capability register (GPIOx_ODRVR) (x=AC,F)</li> <li>6.3.4 GPIO pull-up/pull-down register (GPIOx_PULL) (x=AC,F)</li> <li>6.3.5 GPIO input data register (GPIOx_DDT) (x=AC,F)</li> <li>6.3.6 GPIO output data register (GPIOx_CCF) (x=AC,F)</li> <li>6.3.7 GPIO set/clear register (GPIOx_SCR) (x=AC,F)</li> <li>6.3.8 GPIO multiplexed function low register (GPIOx_MUXL) (x=AC,F)</li> <li>6.3.10 GPIO multiplexed function low register (GPIOx_MUXL) (x=AC,F)</li> <li>6.3.10 GPIO multiplexed function high register (GPIOx_MUXL) (x=AC,F)</li> <li>6.3.12 GPIO port bit toggle register (GPIOx_CLR) (x=AC,F)</li> <li>6.3.13 GPIO huge current control register (GPIOx_HDRV) (x=AC,F)</li> <li>6.3.13 GPIO huge current control register (GPIOx_HDRV) (x=AC,F)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | 6.2.4 Analog input/output configuration 7                              | 74         |

| <ul> <li>6.2.7 IOMUX structure</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | 6.2.5 General-purpose output configuration                             | 74         |

| <ul> <li>6.2.8 Multiplexed function pull-up/pull-down configuration</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        | 6.2.6 GPIO port protection                                             | '5         |

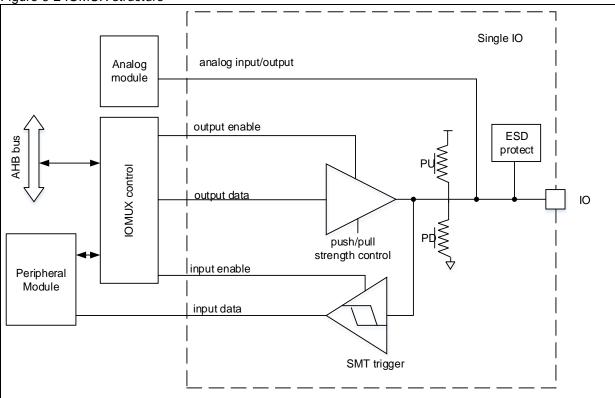

| <ul> <li>6.2.9 IOMUX input/output</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        | 6.2.7 IOMUX structure                                                  | <b>'</b> 5 |

| <ul> <li>6.2.10 Peripheral multiplexed function configuration</li> <li>6.2.11 IOMUX mapping priority</li> <li>6.2.12 External interrupt/wake-up lines</li> <li>6.3 GPIO registers</li> <li>6.3.1 GPIO configuration register (GPIOx_CFGR) (x=AC,F)</li> <li>6.3.2 GPIO output mode register (GPIOx_OMODE) (x=AC,F)</li> <li>6.3.3 GPIO drive capability register (GPIOx_ODRVR) (x=AC,F)</li> <li>6.3.4 GPIO pull-up/pull-down register (GPIOx_PULL) (x=AC,F)</li> <li>6.3.5 GPIO input data register (GPIOx_ODT) (x=AC,F)</li> <li>6.3.6 GPIO output data register (GPIOx_ODT) (x=AC,F)</li> <li>6.3.7 GPIO set/clear register (GPIOx_SCR) (x=AC,F)</li> <li>6.3.8 GPIO multiplexed function low register (GPIOx_MUXL) (x=AC,F)</li> <li>6.3.10 GPIO multiplexed function high register (GPIOx_MUXL) (x=AC,F)</li> <li>6.3.11 GPIO port bit clear register (GPIOx_CLR) (x=AC,F)</li> <li>6.3.12 GPIO port bit toggle register (GPIOx_TOGR) (x=AC,F)</li> <li>6.3.13 GPIO huge current control register (GPIOx_HDRV) (x=AC,F)</li> <li>7 System configuration controller (SCFG)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        | 6.2.8 Multiplexed function pull-up/pull-down configuration             | <b>'</b> 5 |

| <ul> <li>6.2.11 IOMUX mapping priority</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        | 6.2.9 IOMUX input/output 7                                             | <b>'</b> 6 |

| <ul> <li>6.2.12 External interrupt/wake-up lines</li> <li>6.3 GPIO registers</li> <li>6.3.1 GPIO configuration register (GPIOx_CFGR) (x=AC,F)</li> <li>6.3.2 GPIO output mode register (GPIOx_OMODE) (x=AC,F)</li> <li>6.3.3 GPIO drive capability register (GPIOx_ODRVR) (x=AC,F)</li> <li>6.3.4 GPIO pull-up/pull-down register (GPIOx_PULL) (x=AC,F)</li> <li>6.3.5 GPIO input data register (GPIOx_IDT) (x=AC,F)</li> <li>6.3.6 GPIO output data register (GPIOx_SCR) (x=AC,F)</li> <li>6.3.7 GPIO set/clear register (GPIOx_SCR) (x=AC,F)</li> <li>6.3.8 GPIO write protection register (GPIOx_WPR) (x=AC,F)</li> <li>6.3.9 GPIO multiplexed function low register (GPIOx_MUXL) (x=AC,F)</li> <li>6.3.10 GPIO multiplexed function high register (GPIOx_MUXH) (x=AC,F)</li> <li>6.3.12 GPIO port bit clear register (GPIOx_TOGR) (x=AC,F)</li> <li>6.3.13 GPIO huge current control register (GPIOx_HDRV) (x=AC,F)</li> <li>7 System configuration controller (SCFG)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        | 6.2.10 Peripheral multiplexed function configuration                   | 78         |

| <ul> <li>6.3 GPIO registers</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        | 6.2.11 IOMUX mapping priority                                          | 78         |

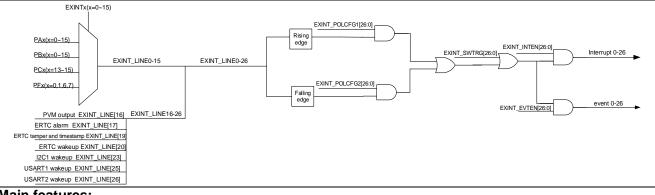

| <ul> <li>6.3.1 GPIO configuration register (GPIOx_CFGR) (x=AC,F)</li> <li>6.3.2 GPIO output mode register (GPIOx_OMODE) (x=AC,F)</li> <li>6.3.3 GPIO drive capability register (GPIOx_ODRVR) (x=AC,F)</li> <li>6.3.4 GPIO pull-up/pull-down register (GPIOx_PULL) (x=AC,F)</li> <li>6.3.5 GPIO input data register (GPIOx_IDT) (x=AC,F)</li> <li>6.3.6 GPIO output data register (GPIOx_ODT) (x=AC,F)</li> <li>6.3.7 GPIO set/clear register (GPIOx_SCR) (x=AC,F)</li> <li>6.3.8 GPIO write protection register (GPIOx_WPR) (x=AC,F)</li> <li>6.3.9 GPIO multiplexed function low register (GPIOx_MUXL) (x=AC,F)</li> <li>6.3.10 GPIO multiplexed function high register (GPIOx_MUXH) (x=AC,F)</li> <li>6.3.11 GPIO port bit clear register (GPIOx_CLR) (x=AC,F)</li> <li>6.3.13 GPIO huge current control register (GPIOx_HDRV) (x=AC,F)</li> <li>7 System configuration controller (SCFG)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        | 6.2.12 External interrupt/wake-up lines                                | 78         |

| <ul> <li>6.3.2 GPIO output mode register (GPIOx_OMODE) (x=AC,F)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6.3    | GPIO registers7                                                        | '8         |

| <ul> <li>6.3.3 GPIO drive capability register (GPIOx_ODRVR) (x=AC,F)</li> <li>6.3.4 GPIO pull-up/pull-down register (GPIOx_PULL) (x=AC,F)</li> <li>6.3.5 GPIO input data register (GPIOx_IDT) (x=AC,F)</li> <li>6.3.6 GPIO output data register (GPIOx_ODT) (x=AC,F)</li> <li>6.3.7 GPIO set/clear register (GPIOx_SCR) (x=AC,F)</li> <li>6.3.8 GPIO write protection register (GPIOx_WPR) (x=AC,F)</li> <li>6.3.9 GPIO multiplexed function low register (GPIOx_MUXL) (x=AC,F)</li> <li>6.3.10 GPIO multiplexed function high register (GPIOx_MUXL) (x=AC,F)</li> <li>6.3.11 GPIO port bit clear register (GPIOx_CLR) (x=AC,F)</li> <li>6.3.12 GPIO port bit toggle register (GPIOx_TOGR) (x=AC,F)</li> <li>6.3.13 GPIO huge current control register (GPIOx_HDRV) (x=AC,F)</li> <li>7 System configuration controller (SCFG)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        | 6.3.1 GPIO configuration register (GPIOx_CFGR) (x=AC,F)                | 79         |

| <ul> <li>6.3.4 GPIO pull-up/pull-down register (GPIOx_PULL) (x=AC,F)</li> <li>6.3.5 GPIO input data register (GPIOx_IDT) (x=AC,F)</li> <li>6.3.6 GPIO output data register (GPIOx_ODT) (x=AC,F)</li> <li>6.3.7 GPIO set/clear register (GPIOx_SCR) (x=AC,F)</li> <li>6.3.8 GPIO write protection register (GPIOx_WPR) (x=AC,F)</li> <li>6.3.9 GPIO multiplexed function low register (GPIOx_MUXL) (x=AC,F)</li> <li>6.3.10 GPIO multiplexed function high register (GPIOx_MUXH) (x=AC,F)</li> <li>6.3.11 GPIO port bit clear register (GPIOx_CLR) (x=AC,F)</li> <li>6.3.12 GPIO port bit toggle register (GPIOx_TOGR) (x=AC,F)</li> <li>6.3.13 GPIO huge current control register (GPIOx_HDRV) (x=AC,F)</li> <li>7 System configuration controller (SCFG)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | 6.3.2 GPIO output mode register (GPIOx_OMODE) (x=AC,F)                 | 79         |

| <ul> <li>6.3.5 GPIO input data register (GPIOx_IDT) (x=AC,F)</li> <li>6.3.6 GPIO output data register (GPIOx_ODT) (x=AC,F)</li> <li>6.3.7 GPIO set/clear register (GPIOx_SCR) (x=AC,F)</li> <li>6.3.8 GPIO write protection register (GPIOx_WPR) (x=AC,F)</li> <li>6.3.9 GPIO multiplexed function low register (GPIOx_MUXL) (x=AC,F)</li> <li>6.3.10 GPIO multiplexed function high register (GPIOx_MUXL) (x=AC,F)</li> <li>6.3.11 GPIO port bit clear register (GPIOx_CLR) (x=AC,F)</li> <li>6.3.12 GPIO port bit toggle register (GPIOx_TOGR) (x=AC,F)</li> <li>6.3.13 GPIO huge current control register (GPIOx_HDRV) (x=AC,F)</li> <li>7 System configuration controller (SCFG)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        | 6.3.3 GPIO drive capability register (GPIOx_ODRVR) (x=AC,F)            | 79         |

| <ul> <li>6.3.6 GPIO output data register (GPIOx_ODT) (x=AC,F)</li> <li>6.3.7 GPIO set/clear register (GPIOx_SCR) (x=AC,F)</li> <li>6.3.8 GPIO write protection register (GPIOx_WPR) (x=AC,F)</li> <li>6.3.9 GPIO multiplexed function low register (GPIOx_MUXL) (x=AC,F)</li> <li>6.3.10 GPIO multiplexed function high register (GPIOx_MUXH) (x=AC,F)</li> <li>6.3.11 GPIO port bit clear register (GPIOx_CLR) (x=AC,F)</li> <li>6.3.12 GPIO port bit toggle register (GPIOx_TOGR) (x=AC,F)</li> <li>6.3.13 GPIO huge current control register (GPIOx_HDRV) (x=AC,F)</li> <li>7 System configuration controller (SCFG)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        | 6.3.4 GPIO pull-up/pull-down register (GPIOx_PULL) (x=AC,F)            | 79         |

| <ul> <li>6.3.7 GPIO set/clear register (GPIOx_SCR) (x=AC,F)</li> <li>6.3.8 GPIO write protection register (GPIOx_WPR) (x=AC,F)</li> <li>6.3.9 GPIO multiplexed function low register (GPIOx_MUXL) (x=AC,F)</li> <li>6.3.10 GPIO multiplexed function high register (GPIOx_MUXH) (x=AC,F)</li> <li>6.3.11 GPIO port bit clear register (GPIOx_CLR) (x=AC,F)</li> <li>6.3.12 GPIO port bit toggle register (GPIOx_TOGR) (x=AC,F)</li> <li>6.3.13 GPIO huge current control register (GPIOx_HDRV) (x=AC,F)</li> <li>7 System configuration controller (SCFG)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        | 6.3.5 GPIO input data register (GPIOx_IDT) (x=AC,F)                    | 79         |

| <ul> <li>6.3.8 GPIO write protection register (GPIOx_WPR) (x=AC,F)</li> <li>6.3.9 GPIO multiplexed function low register (GPIOx_MUXL) (x=AC,F)</li> <li>6.3.10 GPIO multiplexed function high register (GPIOx_MUXH) (x=AC,F)</li> <li>6.3.11 GPIO port bit clear register (GPIOx_CLR) (x=AC,F)</li> <li>6.3.12 GPIO port bit toggle register (GPIOx_TOGR) (x=AC,F)</li> <li>6.3.13 GPIO huge current control register (GPIOx_HDRV) (x=AC,F)</li> <li>7 System configuration controller (SCFG)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | 6.3.6 GPIO output data register (GPIOx_ODT) (x=AC,F) 8                 | 30         |

| <ul> <li>6.3.9 GPIO multiplexed function low register (GPIOx_MUXL) (x=AC,F)</li> <li>6.3.10 GPIO multiplexed function high register (GPIOx_MUXH) (x=AC,I)</li> <li>6.3.11 GPIO port bit clear register (GPIOx_CLR) (x=AC,F)</li> <li>6.3.12 GPIO port bit toggle register (GPIOx_TOGR) (x=AC,F)</li> <li>6.3.13 GPIO huge current control register (GPIOx_HDRV) (x=AC,F)</li> <li>7 System configuration controller (SCFG)</li> <li>7.1 Introduction.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        | 6.3.7 GPIO set/clear register (GPIOx_SCR) (x=AC,F) 8                   | 30         |

| <ul> <li>6.3.10 GPIO multiplexed function high register (GPIOx_MUXH) (x=AC,I</li> <li>6.3.11 GPIO port bit clear register (GPIOx_CLR) (x=AC,F)</li> <li>6.3.12 GPIO port bit toggle register (GPIOx_TOGR) (x=AC,F)</li> <li>6.3.13 GPIO huge current control register (GPIOx_HDRV) (x=AC,F)</li> <li>7 System configuration controller (SCFG)</li> <li>7.1 Introduction.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | 6.3.8 GPIO write protection register (GPIOx_WPR) (x=AC,F) 8            | 30         |

| <ul> <li>6.3.11 GPIO port bit clear register (GPIOx_CLR) (x=AC,F)</li> <li>6.3.12 GPIO port bit toggle register (GPIOx_TOGR) (x=AC,F)</li> <li>6.3.13 GPIO huge current control register (GPIOx_HDRV) (x=AC,F)</li> <li>7 System configuration controller (SCFG)</li> <li>7.1 Introduction.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        | 6.3.9 GPIO multiplexed function low register (GPIOx_MUXL) (x=AC,F).    | 30         |

| <ul> <li>6.3.12 GPIO port bit toggle register (GPIOx_TOGR) (x=AC,F)</li> <li>6.3.13 GPIO huge current control register (GPIOx_HDRV) (x=AC,F)</li> <li>7 System configuration controller (SCFG)</li> <li>7.1 Introduction</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | 6.3.10 GPIO multiplexed function high register (GPIOx_MUXH) (x=AC,F) & | 31         |