# ARM®-based 32-bit Cortex®-M4 MCU with 256 KB Flash, sLib, USBFS, 11 timers, ADC, 2 COMPs, 6 communication interfaces

#### Feature

#### ■ Wireless Bluetooth module

- Dual core Bluetooth® SIG specification 5.0 compliant

- 2.4 GHz low-power transceiver

- Clocks: 16 MHz crystal oscillator, 64 MHz PLL, interal 32 kHz clock

- Peripherals: 8 x GPIOs with 2-channel PWM, 2 x UARTs (UART21 is connected to MCU USART3)

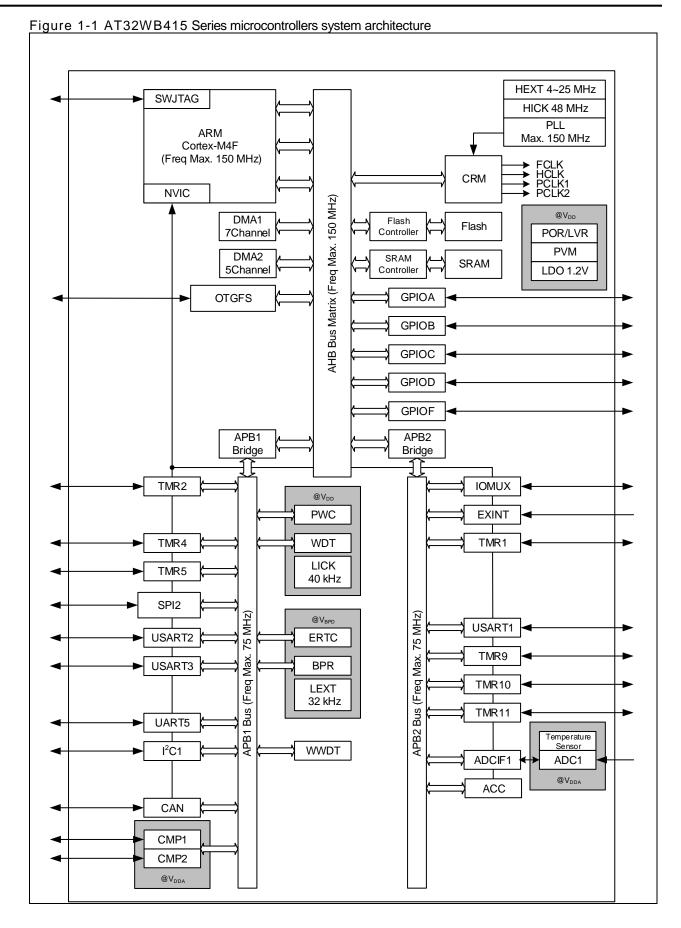

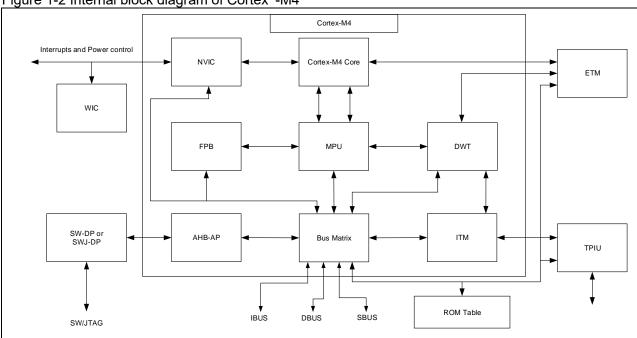

#### ■ Core: ARM®32-bit Cortex®-M4F CPU

- 150 MHz maximum frequency, with a Memory Protection Unit (MPU), single-cycle multiplication and hardware division

- DSP instructions

#### ■ Memories

- 256 KBytes of Flash memory

- 18 Kbytes of boot code area used as a Bootloader or as a general instruction/data memory (one-timeconfigured)

- sLib: configurable part of main Flash set as a library area with code excutable but secured, non-readable

- 32 KBytes of SRAM

#### ■ Power control (PWC)

- 2.6 V ~ 3.6 V application suppy

- Power-on reset (POR)/ low-voltage reset (LVR), and power voltage monitor (PVM)

- Low power: Sleep, Deepsleep, and Standby modes,

- VBAT supply for LEXT, ERTC and 42 x 16-bit battery powered registers (BPR)

#### ■ Clock and reset management (CRM)

- External master clock input

- Internal 48 MHz factory-trimmed clock (HICK), accuracy 1% at T<sub>A</sub>=25 °C, 2.5 % at T<sub>A</sub>=-40 to +105 °C, with automatic clock calibration (ACC)

- PLL with configurable frequency multiplication (31~500) and division factor (1~15)

- 32 kHz crystal oscillator (LEXT)

- Internal 40 kHz RC oscillator (LICK)

#### 1 x 12-bit 0.5 μs A/D converter (up to 16 input channels)

Conversion range: 0 V to 3.6 V

- Sample and hold capability

- Temperature sensor

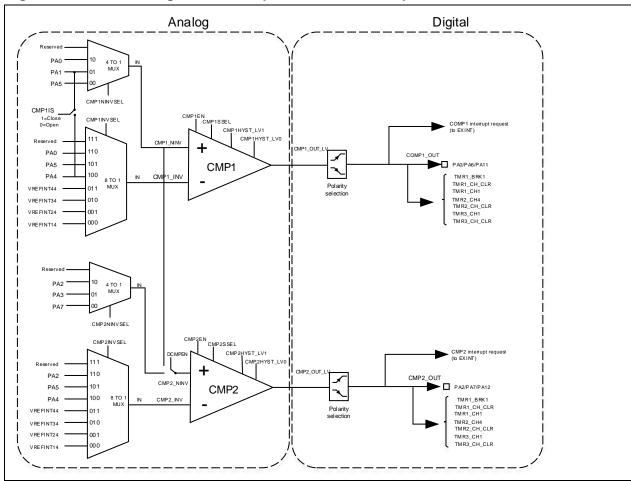

#### 2 x COMP

#### ■ DMA: 12-channel DMA controller

Peripherals supported: timers, ADC, SPI, I<sup>2</sup>C and USART

#### Debug mode

Serial wire debug (SWD)

#### ■ Fast I/O Interfaces

- All mappable to 16 external interrupt vectors

- Almost 5 V-tolerant

- All fast I/Os, registers accessible with fAHB speed

#### ■ Up to 11 Timers (TMR)

- 6 x 16-bit and 1 x 32-bit timers, each with 4 IC/OC/PWM or pulse counter and quadrature (incremental) encoder input

- 2 x Watchdog timers (WDT and WWDT)

- SysTick timer: 24-bit downcounter

#### ■ ERTC: enhanced RTC

#### ■ Up to 6 communication interfaces

- I<sup>2</sup>C interface (SMBus/PMBus)

- Up to 3 x USARTs (ISO7816 interface, LIN, IrDA and modem control)

- SPI interface

- CAN interface (2.0B Active)

- USB full speed interface/host/OTG controller

- Infrared transmitter (IRTMR)

#### **■** CRC Calculation Unit

- 96-bit ID (UID)

- Packaging

- QFN487x7mm

#### **■** List of Models

| Internal Flash | Model           |

|----------------|-----------------|

| 256 KBytes     | AT32WB415CCU7-7 |

#### **Contents**

| 1 | Syste | em architecture                                   | 28 |

|---|-------|---------------------------------------------------|----|

|   | 1.1   | System overview                                   | 30 |

|   |       | 1.1.1 ARM Cortex®-M4 processor                    | 30 |

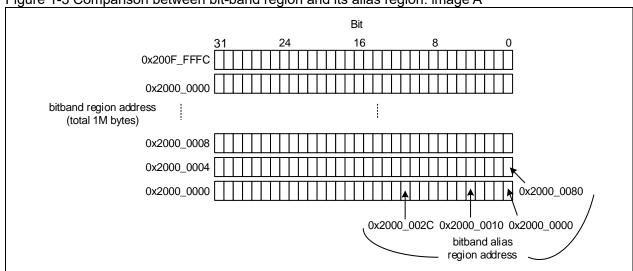

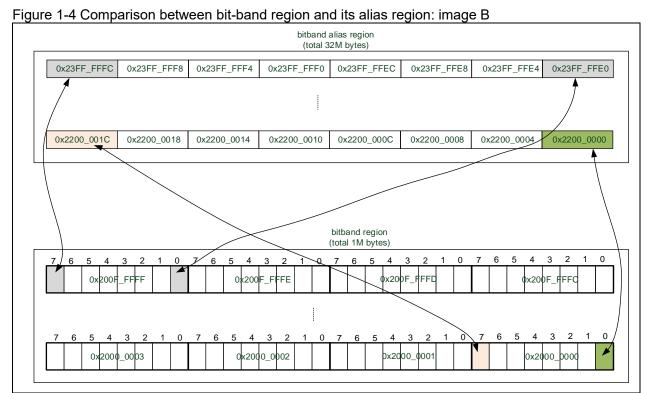

|   |       | 1.1.2 Bit band                                    | 30 |

|   |       | 1.1.3 Interrupt and exception vectors             | 32 |

|   |       | 1.1.4 System Tick (SysTick)                       | 35 |

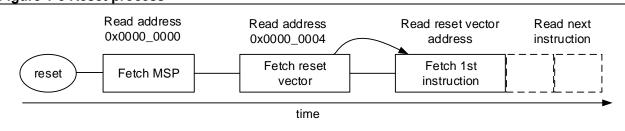

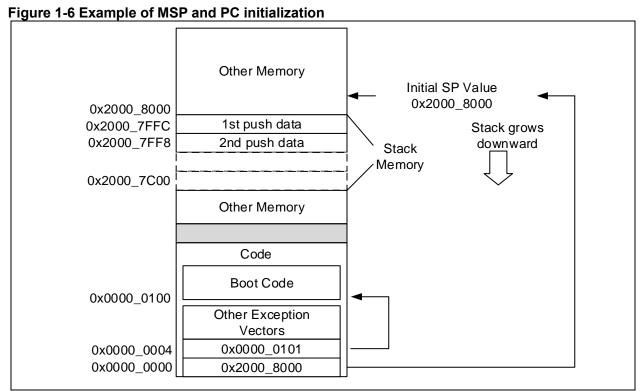

|   |       | 1.1.5 Reset                                       | 35 |

|   | 1.2   | List of abbreviations for registers               | 37 |

|   | 1.3   | Device characteristics information                | 37 |

|   |       | 1.3.1 Flash memory size register                  | 37 |

|   |       | 1.3.2 Device electronic signature                 | 37 |

| 2 | Mem   | ory resources                                     | 38 |

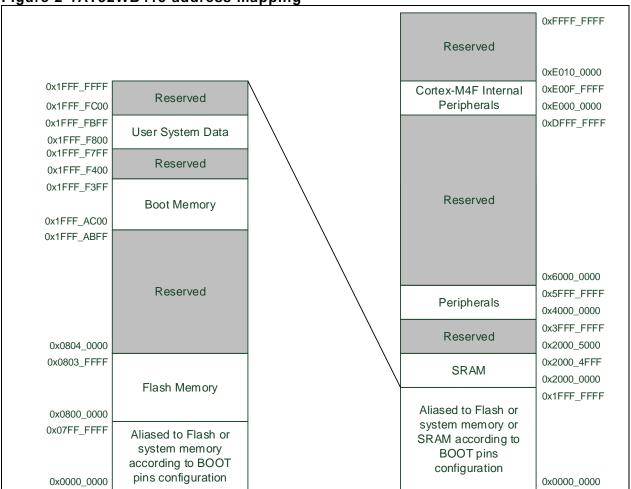

|   | 2.1   | Internal memory address map                       | 38 |

|   | 2.2   | Flash memory                                      | 39 |

|   | 2.3   | SRAM memory                                       | 39 |

|   | 2.4   | Peripheral address map                            | 39 |

| 3 | Powe  | er control (PWC)                                  | 42 |

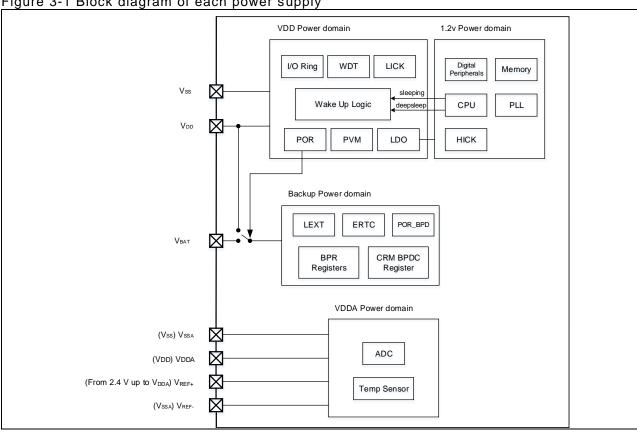

|   | 3.1   | Introduction                                      | 42 |

|   | 3.2   | Main Features                                     | 42 |

|   | 3.3   | POR/LVR                                           | 43 |

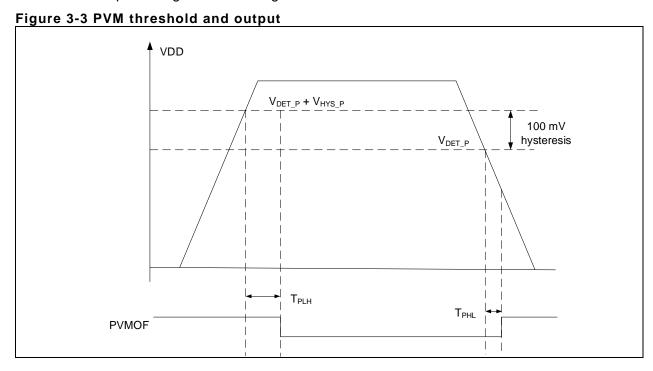

|   | 3.4   | Power voltage monitor (PVM)                       | 43 |

|   | 3.5   | Power domain                                      | 44 |

|   | 3.6   | Power saving modes                                | 44 |

|   | 3.7   | PWC registers                                     |    |

|   |       | 3.7.1 Power control register (PWC_CTRL)           |    |

|   |       | 3.7.2 Power control/status register (PWC_CTRLSTS) |    |

| 4 | Cloc  | k and reset manage (CRM)                          | 48 |

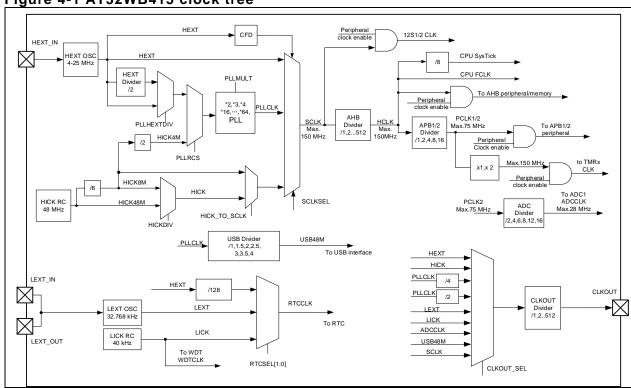

|   | 4.1   | Clock                                             | 48 |

|   |       | 4.1.1 Clock sources                               | 48 |

|   |       |                                                   |    |

|     |       | 4.1.2 System clock                                        | 49 |

|-----|-------|-----------------------------------------------------------|----|

|     |       | 4.1.3 Peripheral clock                                    | 50 |

|     |       | 4.1.4 Clock fail detector                                 | 50 |

|     |       | 4.1.5 Auto step-by-step system clock switch               | 50 |

|     |       | 4.1.6 Internal clock output                               | 51 |

|     |       | 4.1.7 Interrupts                                          | 51 |

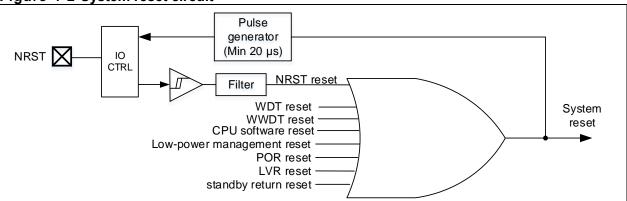

|     | 4.2   | Reset                                                     | 51 |

|     |       | 4.2.1 System reset                                        | 51 |

|     |       | 4.2.2 Battery powered domain reset                        | 51 |

|     | 4.3   | CRM registers                                             | 52 |

|     |       | 4.3.1 Clock control register (CRM_CTRL)                   | 52 |

|     |       | 4.3.2 Clock configuration register (CRM_CFG)              | 53 |

|     |       | 4.3.3 Clock interrupt register (CRM_CLKINT)               | 55 |

|     |       | 4.3.4 APB2 peripheral reset register (CRM_APB2RST)        | 56 |

|     |       | 4.3.5 APB1 peripheral reset register1 (CRM_APB1RST)       | 57 |

|     |       | 4.3.6 APB peripheral clock enable register (CRM_AHBEN)    | 57 |

|     |       | 4.3.7 APB2 peripheral clock enable register (CRM_AHB2EN)  | 58 |

|     |       | 4.3.8 APB1 peripheral clock enable register (CRM_AHB1EN)  | 59 |

|     |       | 4.3.9 Battery powered domain control register (CRM_BPDC)  | 60 |

|     |       | 4.3.10 Control/status register (CRM_CTRLSTS)              | 60 |

|     |       | 4.3.11 APB peripheral reset register (CRM_APBRST)         | 61 |

|     |       | 4.3.12 PLL configuration register (CRM_PLL)               | 61 |

|     |       | 4.3.13 Additional register (CRM_MISC1)                    | 62 |

|     |       | 4.3.14 OTG_FS extended control register (CRM_OTG_EXTCTRL) | 62 |

|     |       | 4.3.15 Additional register (CRM_MISC2)                    | 63 |

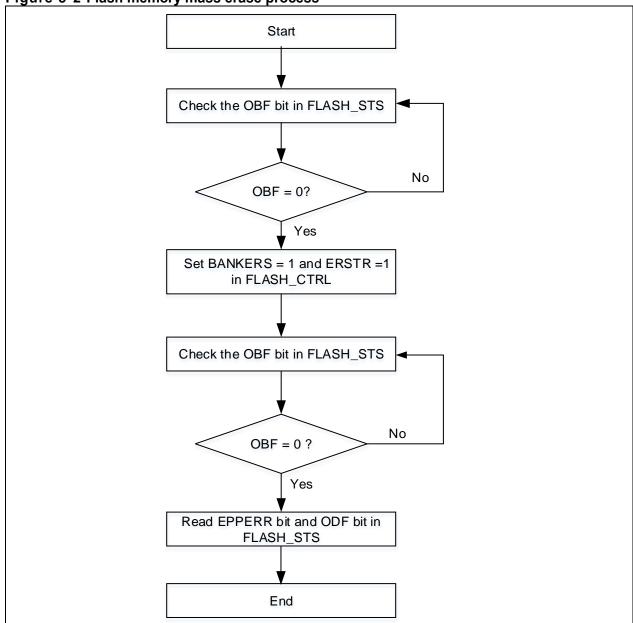

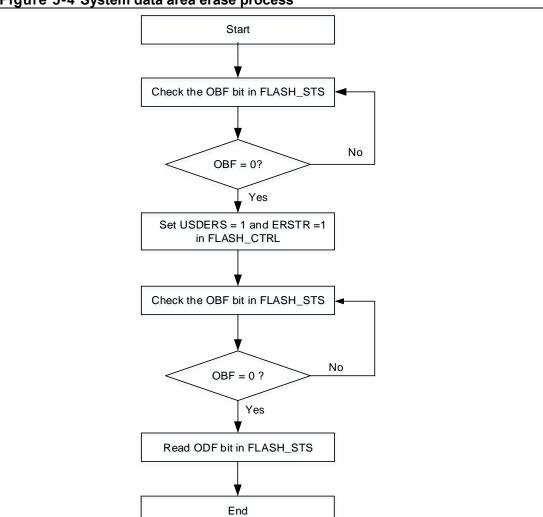

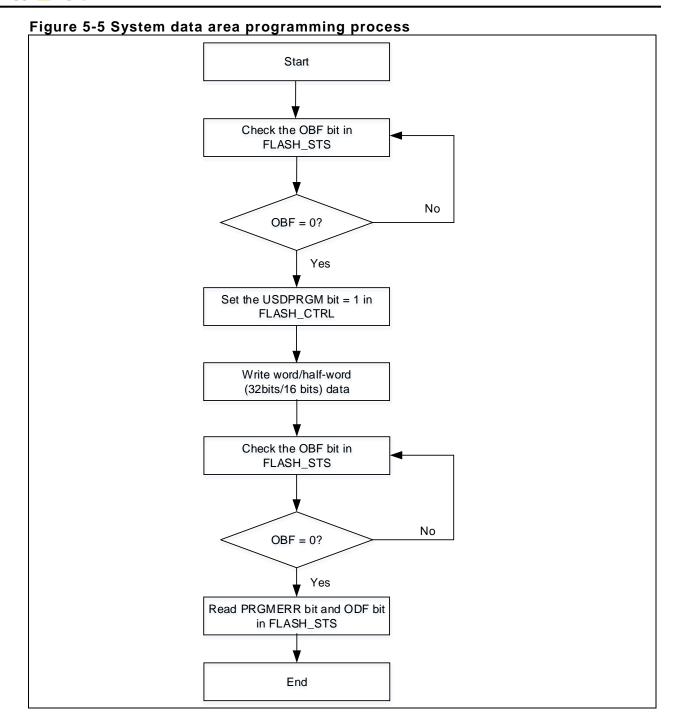

| 5 F | Flash | memory controller (FLASH)                                 | 64 |

|     | 5.1   | FLASH introduction                                        |    |

|     | 5.2   | Flash memory operation                                    |    |

|     | 5.2   | 5.2.1 Unlock/lock                                         |    |

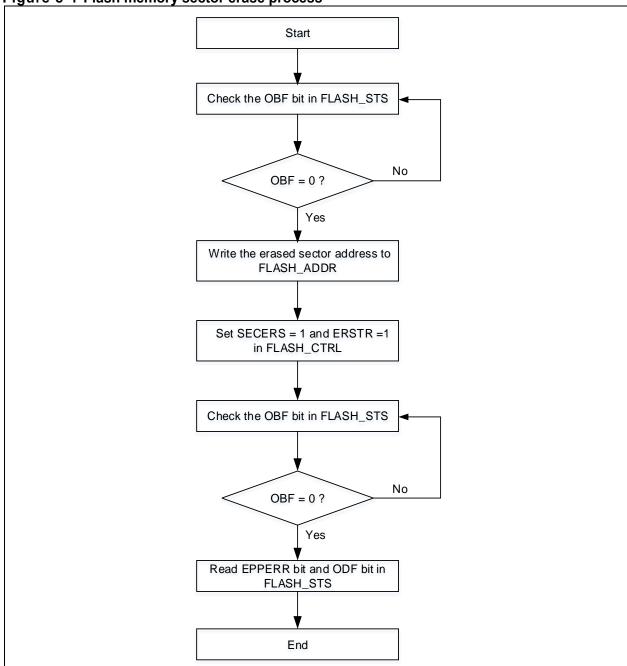

|     |       | 5.2.2 Erase operation                                     |    |

|     |       | 5.2.3 Programming operation                               |    |

|     |       | 5.2.4 Read operation                                      |    |

|     | 5.3   | Main Flash memory extension area                          |    |

|     | 5.4   | User system data area                                     |    |

|     | ა.4   | User system data area                                     | 09 |

6

|      | 5.4.1 Unlock/lock                                                     |

|------|-----------------------------------------------------------------------|

|      | 5.4.2 Erase operation                                                 |

|      | 5.4.3 Programming operation                                           |

|      | 5.4.4 Read operation                                                  |

| 5.5  | Flash memory protection                                               |

|      | 5.5.1 Access protection                                               |

|      | 5.5.2 Erase/program protection                                        |

| 5.6  | Special functions                                                     |

|      | 5.6.1 Security library settings                                       |

|      | 5.6.2 Bootloader code area used as Flash memory extension             |

|      | 5.6.3 CRC verify                                                      |

| 5.7  | Flash memory registers                                                |

|      | 5.7.1 Flash performance select register (FLASH_PSR)                   |

|      | 5.7.2 Flash unlock register (FLASH_UNLOCK)                            |

|      | 5.7.3 Flash user system data unlock register (FLASH_USD_UNLOCK) 76    |

|      | 5.7.4 Flash status register (FLASH_STS)                               |

|      | 5.7.5 Flash control register (FLASH_CTRL)                             |

|      | 5.7.6 Flash address register (FLASH_ADDR)                             |

|      | 5.7.7 User system data register (FLASH_USD)                           |

|      | 5.7.8 Erase/program protection status register (FLASH_EPPS)           |

|      | 5.7.9 Flash security library status register0 (SLIB_STS0)             |

|      | 5.7.10 Flash security library status register1 (SLIB_STS1)            |

|      | 5.7.11 Security library password clear register (SLIB_PWD_CLR) 79     |

|      | 5.7.12 Security library additional status register (SLIB_MISC_STS) 79 |

|      | 5.7.13 Flash CRC address register (FLASH_CRC_ARR)                     |

|      | 5.7.14 Flash CRC control register (FLASH_CRC_CTRL) 80                 |

|      | 5.7.15 Flash CRC check result register (FLASH_CRC_CHKR) 80            |

|      | 5.7.16 Security library password setting register (SLIB_SET_PWD) 80   |

|      | 5.7.17 Security library address setting register (SLIB_SET_RANGE) 80  |

|      | 5.7.18 Flash extension memory security library setting register       |

|      | (EM_SLIB_SET)                                                         |

|      | 5.7.19 Boot mode setting register (BTM_MODE_SET)                      |

|      | 5.7.20 Security library unlock register (FLASH_UNLOCK)                |

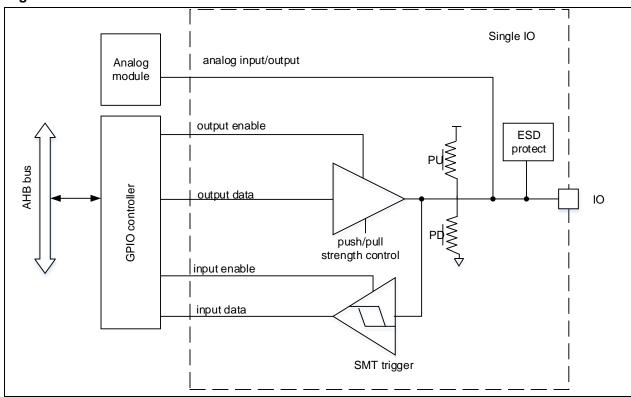

| Gene | ral-purpose I/Os (GPIOs)83                                            |

|   | 6.1   | Introduction                                                          | 83   |

|---|-------|-----------------------------------------------------------------------|------|

|   | 6.2   | Functional overview                                                   | 83   |

|   |       | 6.2.1 GPIO structure                                                  | 83   |

|   |       | 6.2.2 GPIO reset status                                               | 83   |

|   |       | 6.2.3 General-purpose input configuration                             | 84   |

|   |       | 6.2.4 Analog input/output configuration                               | 84   |

|   |       | 6.2.5 General-purpose output configuration                            | 84   |

|   |       | 6.2.6 GPIO port protection                                            | 84   |

|   | 6.3   | GPIO registers                                                        | 84   |

|   |       | 6.3.1 GPIO configuration register low (GPIOx_CFGLR) (x=AF)            | 85   |

|   |       | 6.3.2 GPIO configuration register high (GPIOx_CFGHR) (x=AF)           | 85   |

|   |       | 6.3.3 GPIO input register (GPIOx_IDT) (x=AF)                          | 85   |

|   |       | 6.3.4 GPIO output register (GPIOx_ODT) (x= AF)                        | 86   |

|   |       | 6.3.5 GPIO set/clear register (GPIOx_SCR) (x=AF)                      | 86   |

|   |       | 6.3.6 GPIO bit clear register (GPIOx_CLR) (x=AF)                      | 86   |

|   |       | 6.3.7 GPIO write protection register (GPIOx_WPR) (x=AF)               | 86   |

| 7 | Multi | iplexed function I/Os (IOMUX)                                         | 87   |

|   | 7.1   | Introduction                                                          | 87   |

|   | 7.2   | Functional overview                                                   | 87   |

|   |       | 7.2.1 IOMUX structure                                                 | 87   |

|   |       | 7.2.2 MUX Input configuration                                         | 88   |

|   |       | 7.2.3 MUX output or bidirectional MUX configuration                   | 88   |

|   |       | 7.2.4 Peripheral MUX function configuration                           | 88   |

|   |       | 7.2.5 IOMUX map priority                                              | 88   |

|   |       | 7.2.5.1 Hardware preemption                                           | . 89 |

|   |       | 7.2.5.2 Debug port priority                                           |      |

|   |       | 7.2.5.3 Other peripheral output priority                              |      |

|   |       | 7.2.6 External interrupt/wake-up lines                                |      |

|   | 7.3   | IOMUX registers                                                       |      |

|   |       | 7.3.1 Event output control register (IOMUX_EVTOUT)                    |      |

|   |       | 7.3.2 IOMUX remap register (IOMUX_REMAP)                              |      |

|   |       | 7.3.3 IOMUX external interrupt configuration register1 (IOMUX_EXINTC1 | •    |

|   |       | 7.3.4 IOMUX external interrupt configuration register2 (IOMUX_EXINTC2 | •    |

|   |       | 7.3.5 IOMUX external interrupt configuration register3 (IOMUX_EXINTC3 | 1194 |

|   |      | 7.3.6 IOMUX external interrupt configuration register4 (IOMUX_EXINTC4)95 |

|---|------|--------------------------------------------------------------------------|

|   |      | 7.3.7 IOMUX remap register2 (IOMUX_REMAP2)                               |

|   |      | 7.3.8 IOMUX remap register3 (IOMUX_REMAP3)                               |

|   |      | 7.3.9 IOMUX remap register4 (IOMUX_REMAP4)                               |

|   |      | 7.3.10 IOMUX remap register5 (IOMUX_REMAP5) 97                           |

|   |      | 7.3.11 IOMUX remap register6 (IOMUX_REMAP6) 97                           |

|   |      | 7.3.12 IOMUX remap register7 (IOMUX_REMAP7)                              |

|   |      | 7.3.13 IOMUX remap register8 (IOMUX_REMAP8)                              |

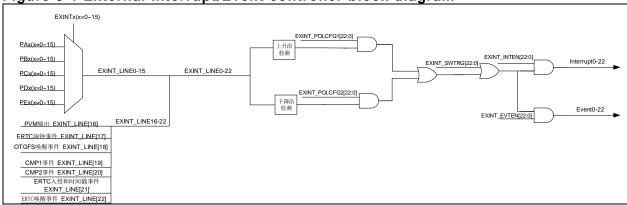

| 8 | Exte | rnal interrupt/Event controller (EXINT) 100                              |

|   | 8.1  | EXINT introduction                                                       |

|   | 8.2  | Function overview and configuration procedure                            |

|   | 8.3  | EXINT registers                                                          |

|   |      | 8.3.1 Interrupt enable register (EXINT_INTEN)101                         |

|   |      | 8.3.2 Event enable register (EXINT_EVTEN)101                             |

|   |      | 8.3.3 Polarity configuration register1 (EXINT_ POLCFG1)101               |

|   |      | 8.3.4 Polarity configuration register2 (EXINT_ POLCFG2)102               |

|   |      | 8.3.5 Software trigger register (EXINT_ SWTRG)102                        |

|   |      | 8.3.6 Interrupt status register (EXINT_ INTSTS)102                       |

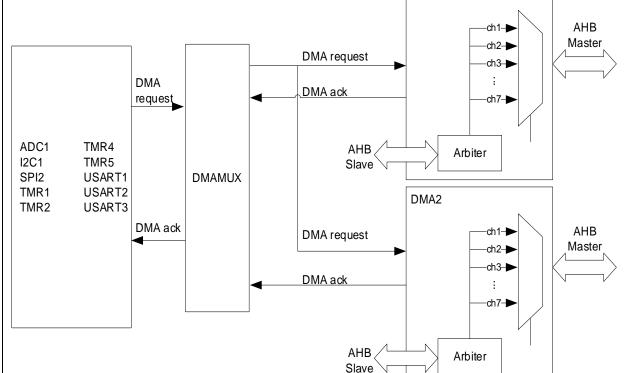

| 9 | DMA  | controller (DMA)                                                         |

|   | 9.1  | Introduction                                                             |

|   | 9.2  | Main features                                                            |

|   | 9.3  | Function overview104                                                     |

|   |      | 9.3.1 DMA configuration104                                               |

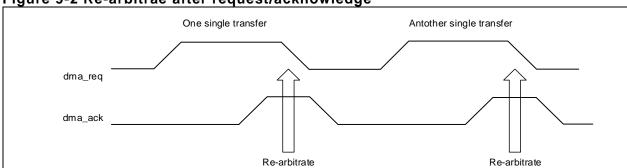

|   |      | 9.3.2 Handshake mechanism104                                             |

|   |      | 9.3.3 Arbiter                                                            |

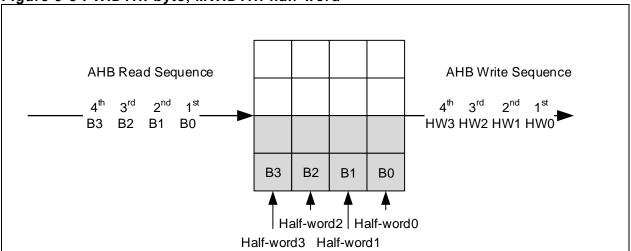

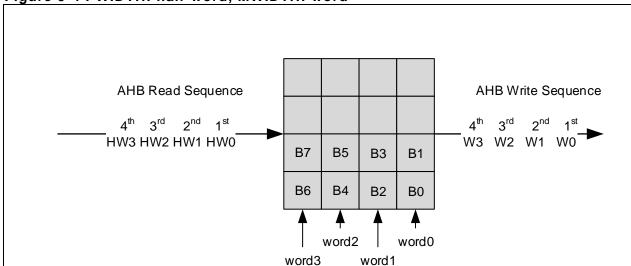

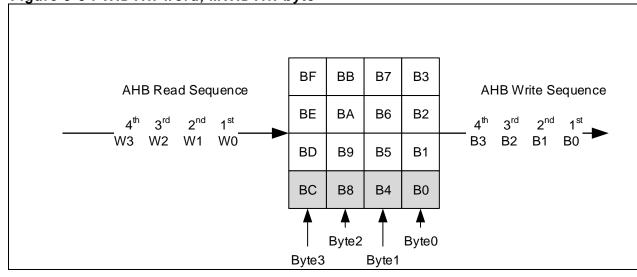

|   |      | 9.3.4 Programmable data transfer width                                   |

|   |      | 9.3.5 Errors                                                             |

|   |      | 9.3.6 Interrupts106                                                      |

|   |      | 9.3.7 Fixed DMA request mapping106                                       |

|   |      | 9.3.8 Flexible DMA request mapping106                                    |

|   | 9.4  | DMA registers                                                            |

|   |      | 9.4.1 DMA interrupt status register (DMA_STS)109                         |

|   |      | 9.4.2 DMA interrupt flag clear register (DMA_CLR)110                     |

|    |                     | 9.4.3 DMA channel-x configuration register (DMA_CxCTRL) (x = 17     | )112   |

|----|---------------------|---------------------------------------------------------------------|--------|

|    |                     | 9.4.4 DMA channel-x number of data register (DMA_CxDTCNT) ( $x = 1$ | 7)113  |

|    |                     | 9.4.5 DMA channel-x peripheral address register                     |        |

|    |                     | (DMA_CxPADDR) (x = 17)                                              | 113    |

|    |                     | 9.4.6 DMA channel-x memory address register (DMA_CxMADDR) (x =      | 17)114 |

|    |                     | 9.4.7 DMA channel source register (DMA_SRC_SEL0)                    | 114    |

|    |                     | 9.4.8 DMA channel source register1 (DMA_SRC_SEL1)                   | 114    |

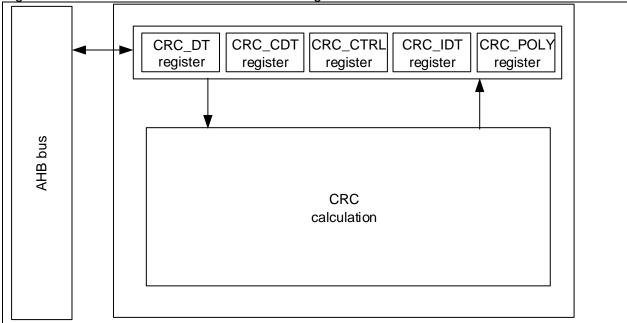

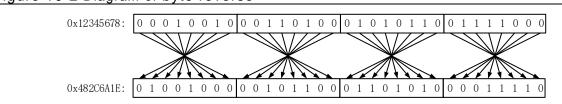

| 10 | CRC                 | calculation unit (CRC)                                              | . 115  |

|    | 10.1                | CRC introduction                                                    | 115    |

|    | 10.2                | CRC functional description                                          | 115    |

|    | 10.3                | CRC registers                                                       | 116    |

|    |                     | 10.3.1 Data register (CRC_DT)                                       | 116    |

|    |                     | 10.3.2 Common data register (CRC_CDT)                               | 116    |

|    |                     | 10.3.3 Control register (CRC_CTRL)                                  | 117    |

|    |                     | 10.3.4 Initialization register (CRC_IDT)                            | 117    |

|    |                     | 10.3.5 Initialization register (CRC_IDT)                            | 117    |

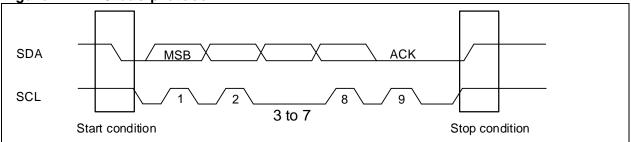

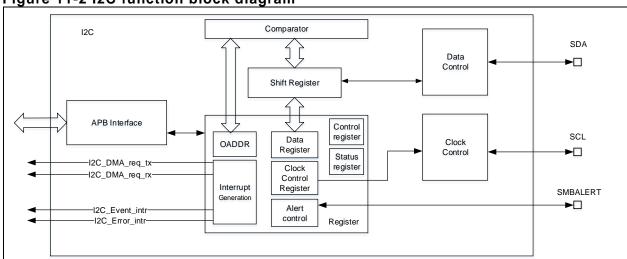

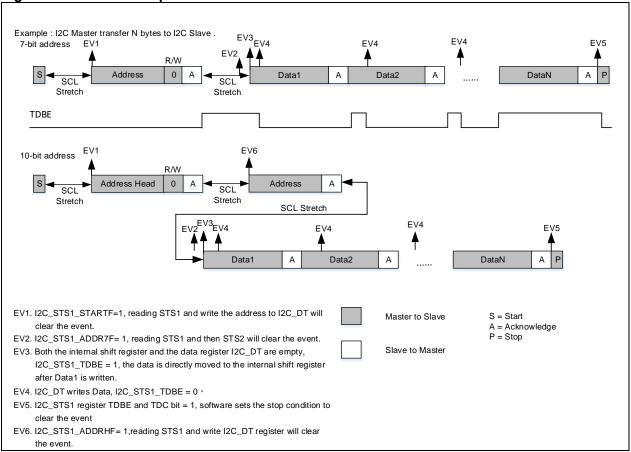

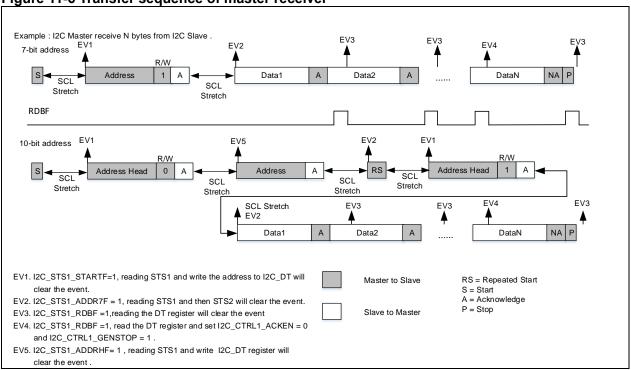

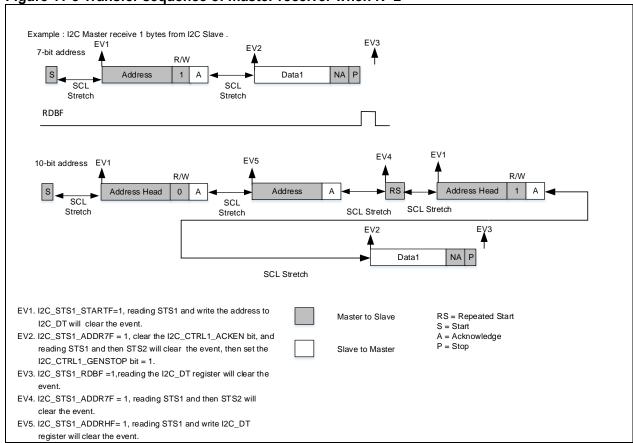

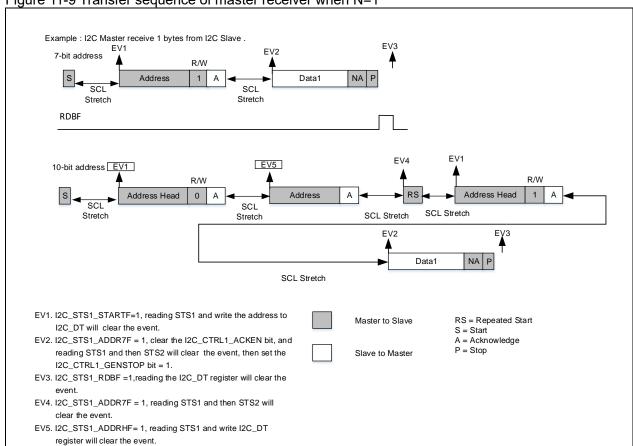

| 11 | I <sup>2</sup> C in | terface                                                             | . 118  |

|    | 11.1                | I <sup>2</sup> C introduction                                       | 118    |

|    | 11.2                | I <sup>2</sup> C main features                                      | 118    |

|    | 11.3                | I <sup>2</sup> C function overview                                  | 118    |

|    | 11.4                | I <sup>2</sup> C interface                                          | 119    |

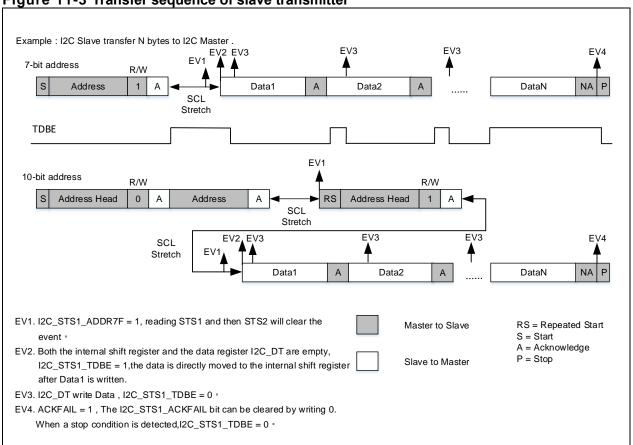

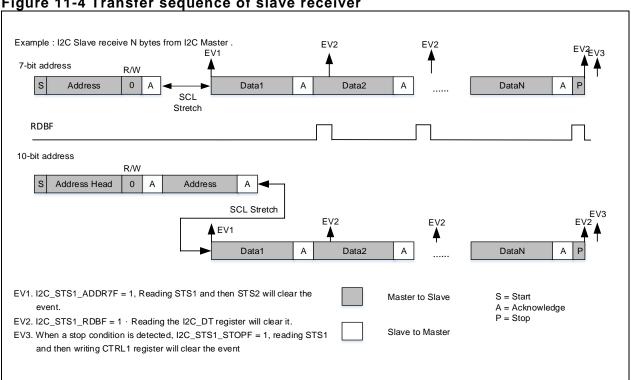

|    |                     | 11.4.1 I <sup>2</sup> C slave communication flow                    | 121    |

|    |                     | 11.4.2 I <sup>2</sup> C master communication flow                   | 122    |

|    |                     | 11.4.3 Data transfer using DMA                                      | 128    |

|    |                     | 11.4.4 SMBus                                                        | 129    |

|    |                     | 11.4.5 I <sup>2</sup> C interrupt requests                          | 131    |

|    |                     | 11.4.6 I <sup>2</sup> C debug mode                                  | 131    |

|    | 11.5                | I <sup>2</sup> C registers                                          | 131    |

|    |                     | 11.5.1 Control register1 (I2C_CTRL1)                                | 132    |

|    |                     | 11.5.2 Control register2 (I2C_CTRL2)                                | 133    |

|    |                     | 11.5.3 Own address register1 (I2C_OADDR1)                           | 134    |

|    |                     | 11.5.4 Own address register2 (I2C_OADDR2)                           | 134    |

|    |                     | 11.5.5 Data register (I2C_DT)                                       | 134    |

1

|   |       | 11.5.6 Status register1 (I2C_STS1)                   | 135           |

|---|-------|------------------------------------------------------|---------------|

|   |       | 11.5.7 Status register2 (I2C_STS2)                   | 137           |

|   |       | 11.5.8 Clock control register (I2C_ CLKCTRL)         | 137           |

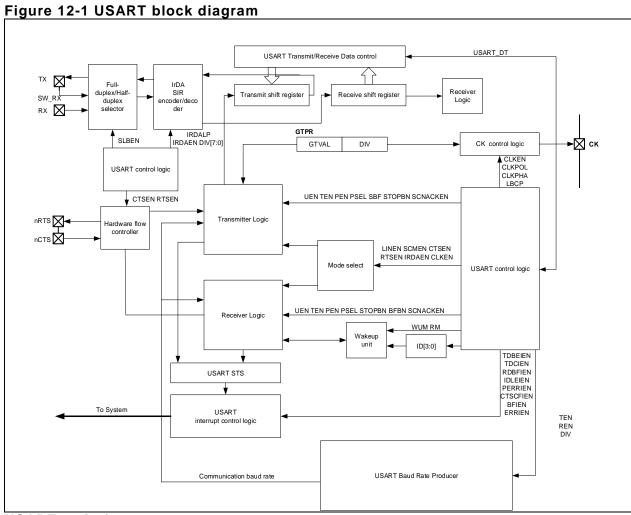

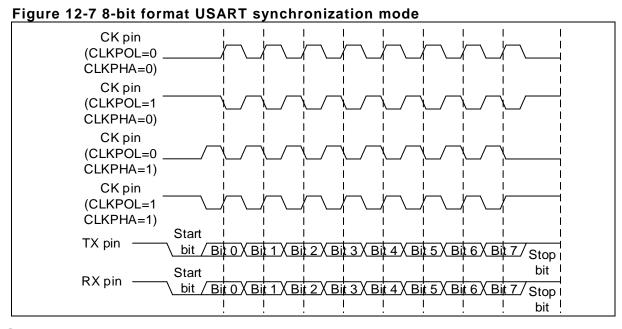

| 2 | Unive | ersal synchronous/asynchronous receiver/transmitte   | er (USART)139 |

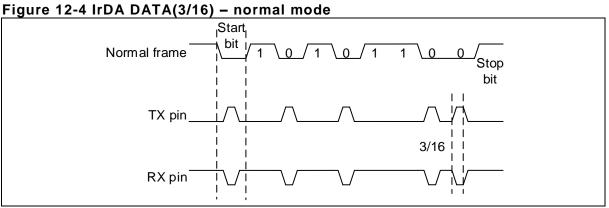

|   | 12.1  | USART introduction                                   | 139           |

|   | 12.2  | Full-duplex/half-duplex selector                     | 141           |

|   | 12.3  | Mode selector                                        | 141           |

|   |       | 12.3.1 Introduction                                  | 141           |

|   |       | 12.3.2 Configuration procedure                       | 141           |

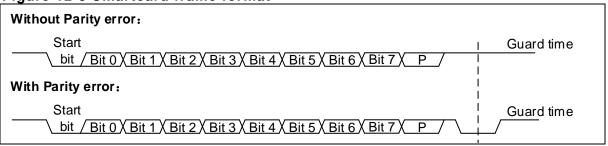

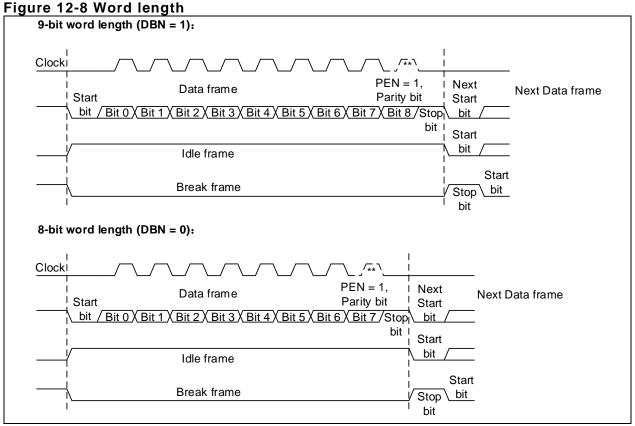

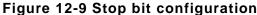

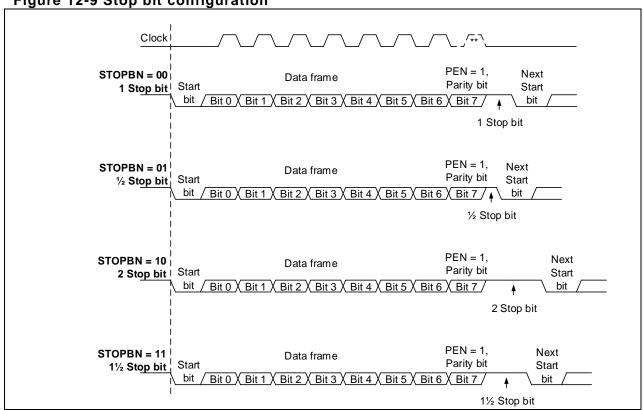

|   | 12.4  | USART frame format and configuration                 | 144           |

|   | 12.5  | DMA transfer introduction                            | 146           |

|   |       | 12.5.1 Transmission using DMA                        | 146           |

|   |       | 12.5.2 Reception using DMA                           | 146           |

|   | 12.6  | Baud rate generation                                 | 147           |

|   |       | 12.6.1 Introduction                                  | 147           |

|   |       | 12.6.2 Configuration                                 | 147           |

|   | 12.7  | Transmitter                                          | 147           |

|   |       | 12.7.1 Transmitter introduction                      | 147           |

|   |       | 12.7.2 Transmitter configuration                     | 149           |

|   | 12.8  | Receiver                                             | 149           |

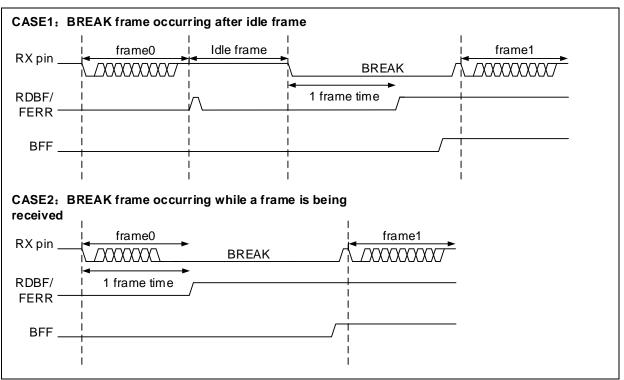

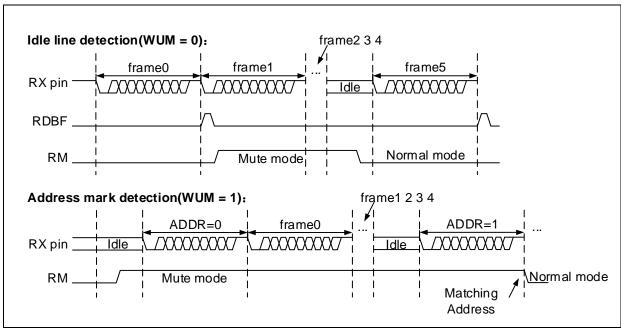

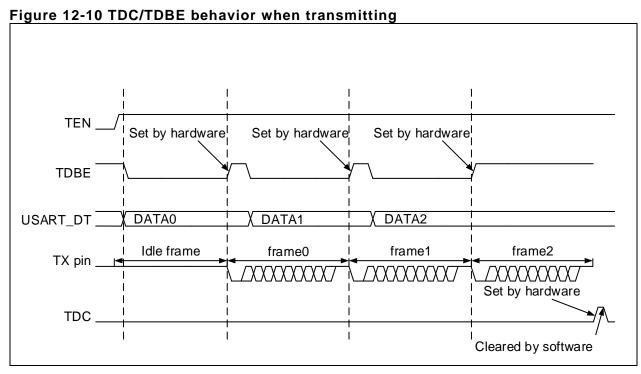

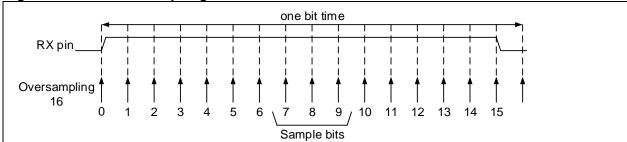

|   |       | 12.8.1 Receiver introduction                         | 149           |

|   |       | 12.8.2 Receiver configuration                        | 150           |

|   |       | 12.8.3 Start bit and noise detection                 | 151           |

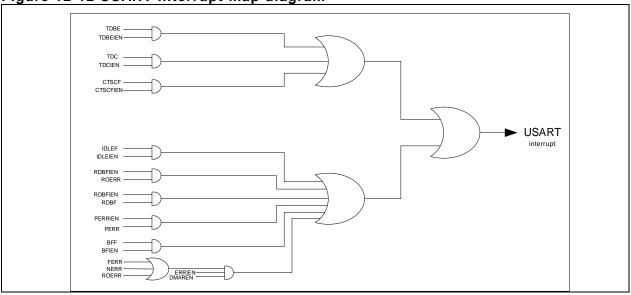

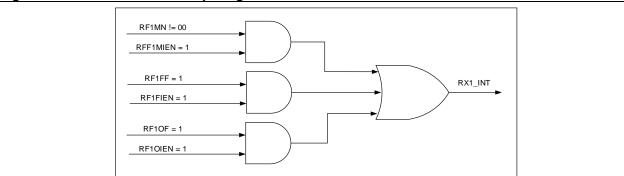

|   | 12.9  | Interrupt requests                                   | 152           |

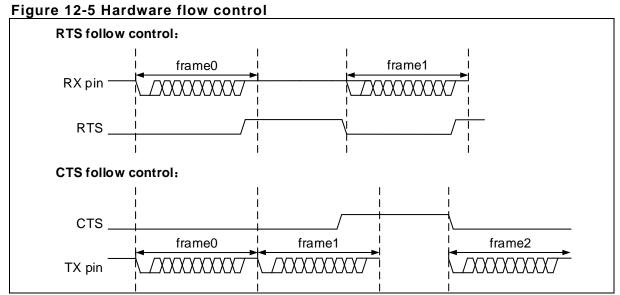

|   | 12.10 | OI/O pin control                                     | 152           |

|   | 12.1  | 1USART registers                                     | 154           |

|   |       | 12.11.1 Status register (USART_STS)                  | 154           |

|   |       | 12.11.2 Data register (USART_DT)                     | 155           |

|   |       | 12.11.3 Baud rate register (USART_BAUDR)             | 155           |

|   |       | 12.11.4 Control register1 (USART_CTRL1)              | 155           |

|   |       | 12.11.5 Control register2 (USART_CTRL2)              | 157           |

|   |       | 12.11.6 Control register3 (USART_CTRL3)              | 158           |

|   |       | 12.11.7 Guard time and divider register (USART_GDIV) | 159           |

| 13 | Seria | I peripheral interface (SPI)             | 160 |

|----|-------|------------------------------------------|-----|

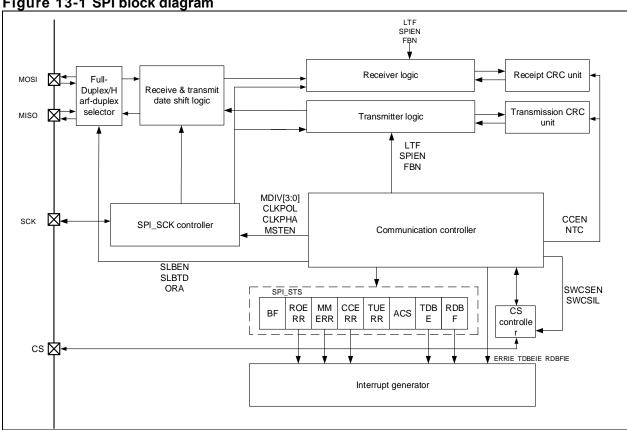

|    | 13.1  | SPI introduction                         | 160 |

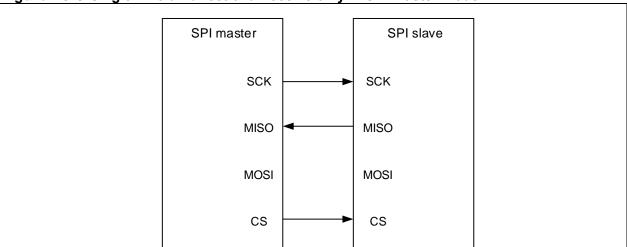

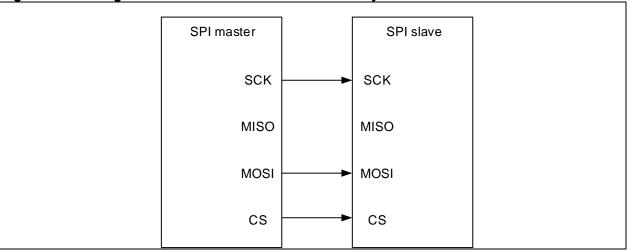

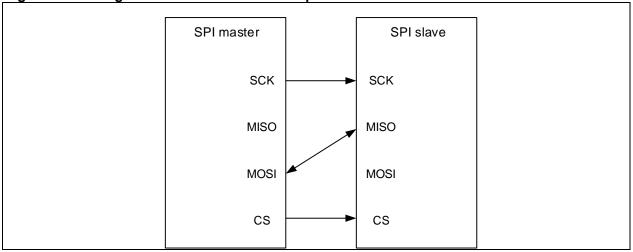

|    | 13.2  | Functional overview                      | 160 |

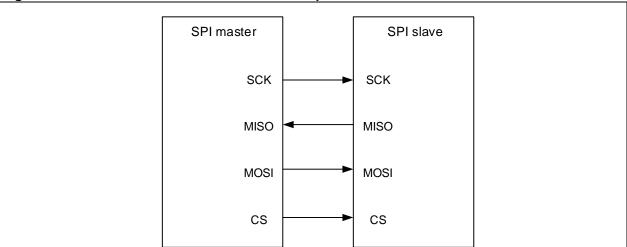

|    |       | 13.2.1 SPI description                   | 160 |

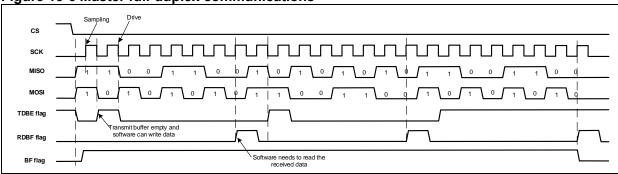

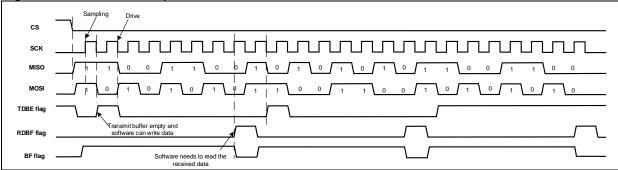

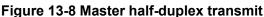

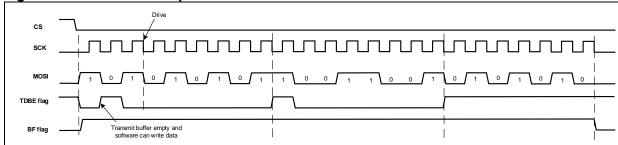

|    |       | 13.2.2 Full-duplex/half-duplex selector  | 161 |

|    |       | 13.2.3 Chip select controller            | 163 |

|    |       | 13.2.4 SPI_SCK controller                | 163 |

|    |       | 13.2.5 CRC introduction                  | 163 |

|    |       | 13.2.6 DMA transfer                      | 164 |

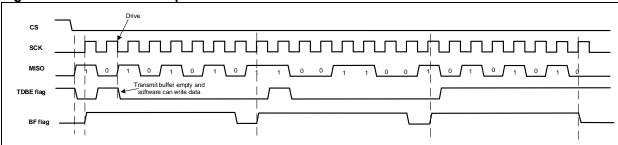

|    |       | 13.2.7 Transmitter                       | 165 |

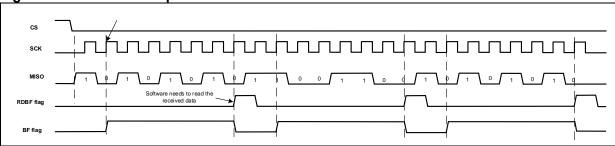

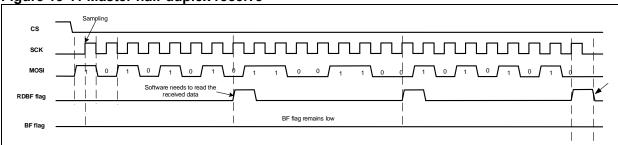

|    |       | 13.2.8 Receiver                          | 165 |

|    |       | 13.2.9 Motorola mode                     | 166 |

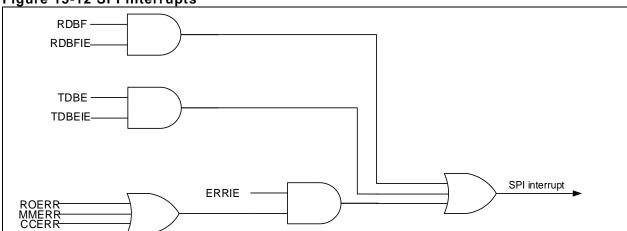

|    |       | 13.2.10 Interrupts                       | 168 |

|    |       | 13.2.11 IO pin control                   | 169 |

|    |       | 13.2.12 Precautions                      | 169 |

|    | 13.3  | SPI registers                            | 169 |

|    |       | 13.3.1 SPI control register1 (SPI_CTRL1) | 169 |

|    |       | 13.3.2 SPI control register2 (SPI_CTRL2) | 170 |

|    |       | 13.3.3 SPI status register (SPI_STS)     | 171 |

|    |       | 13.3.4 SPI data register (SPI_DT)        | 171 |

|    |       | 13.3.5 SPICRC register (SPI_CPOLY)       | 172 |

|    |       | 13.3.6 SPIRxCRC register (SPI_RCRC)      | 172 |

|    |       | 13.3.7 SPITxCRC register (SPI_TCRC)      | 172 |

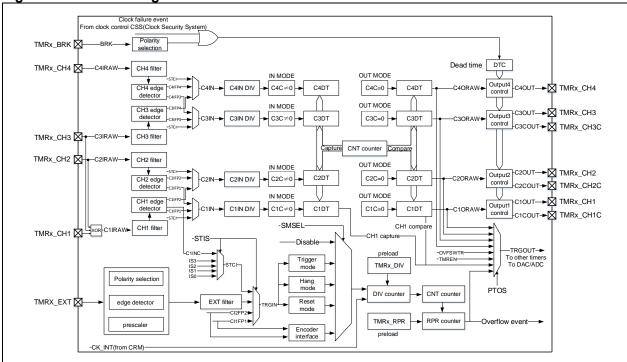

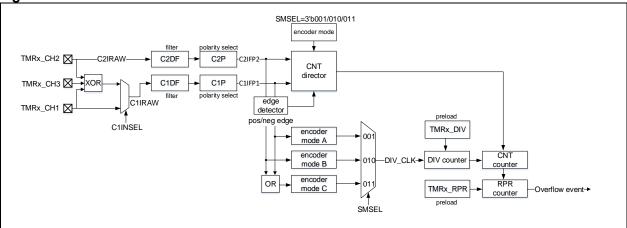

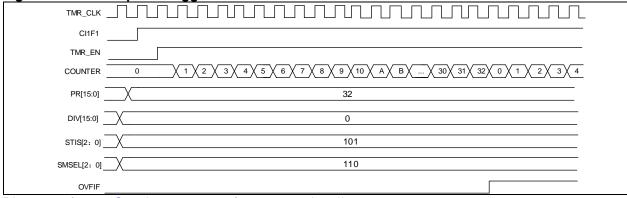

| 14 | Time  | r                                        | 173 |

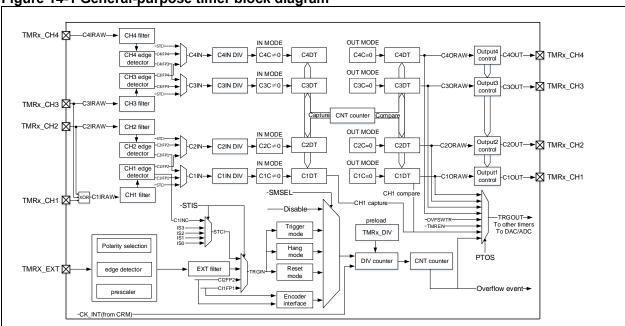

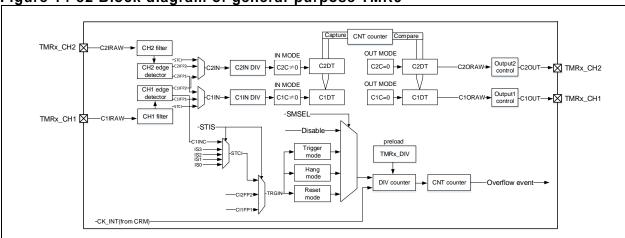

|    | 14.1  | General-purpose timer (TMR2 to TMR5)     | 173 |

|    |       | 14.1.1 TMRx introduction                 | 173 |

|    |       | 14.1.2 TMRx main features                | 174 |

|    |       | 14.1.3 TMRx functional overview          | 174 |

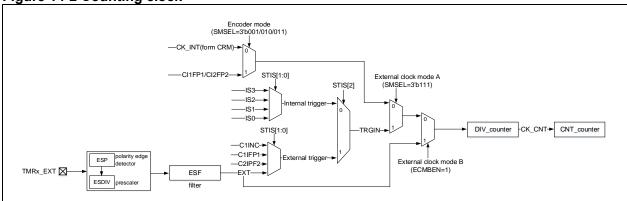

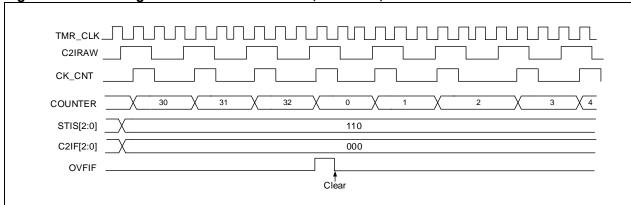

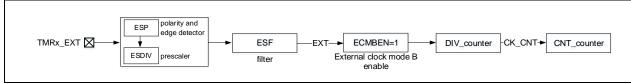

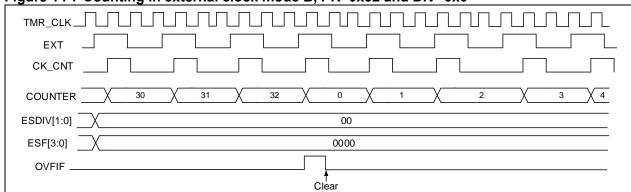

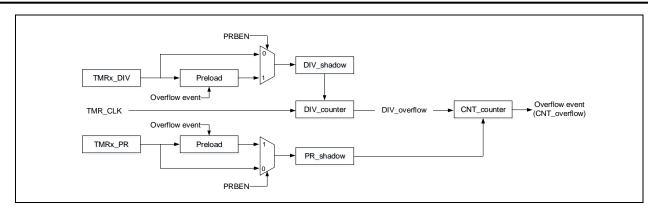

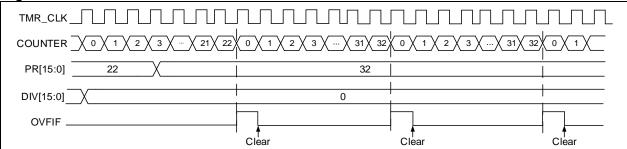

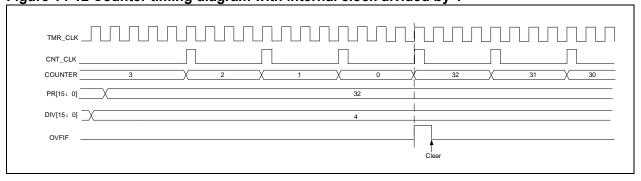

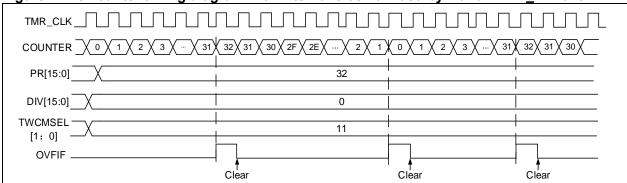

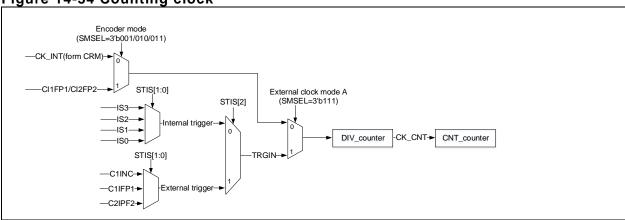

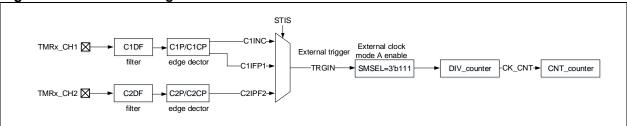

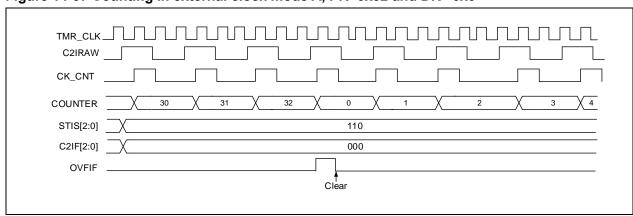

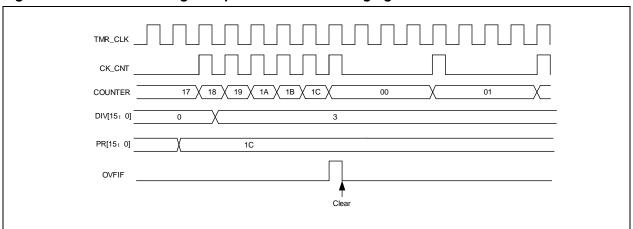

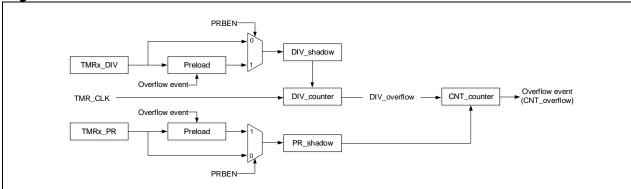

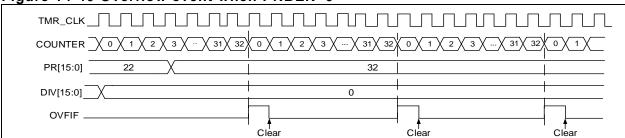

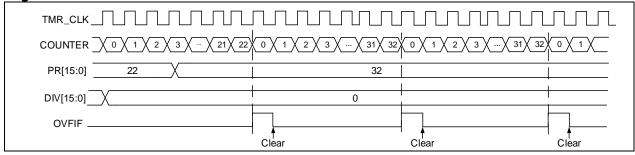

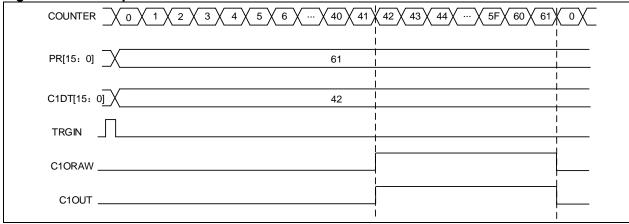

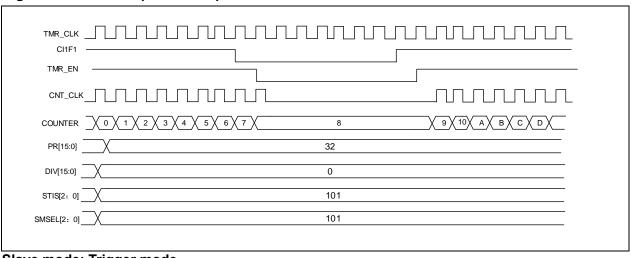

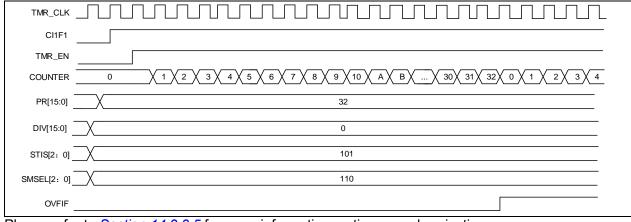

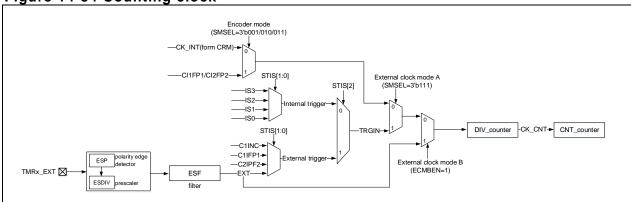

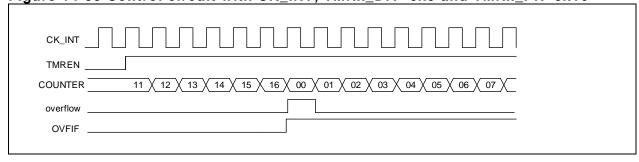

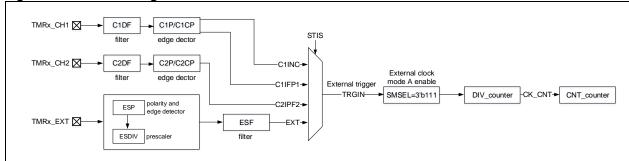

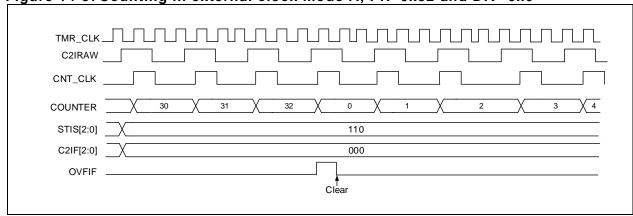

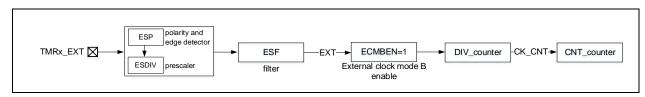

|    |       | 14.1.3.1 Counting clock                  | 174 |

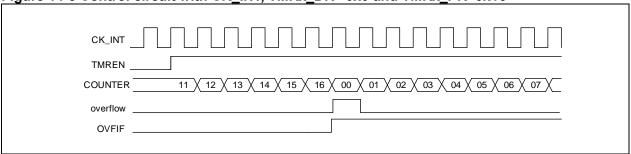

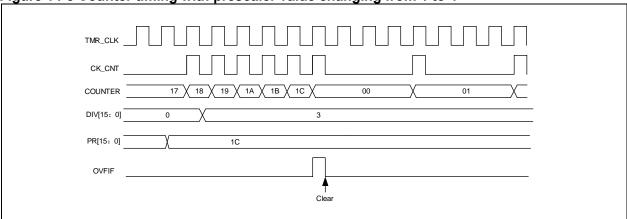

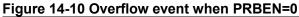

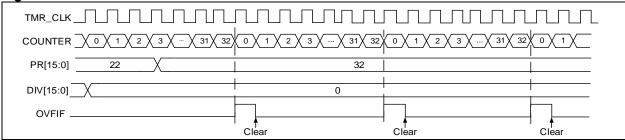

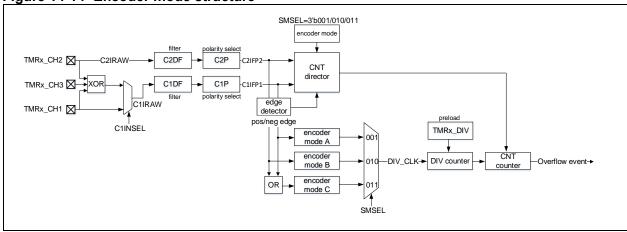

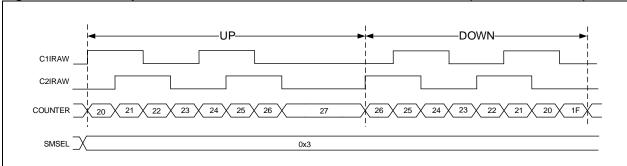

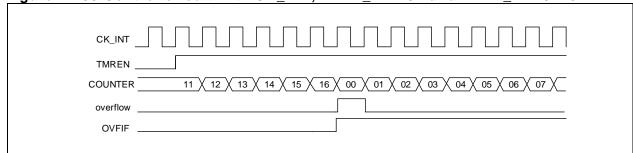

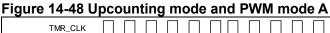

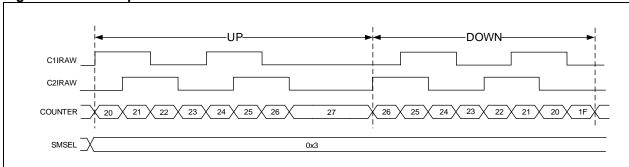

|    |       | 14.1.3.2 Counting mode                   | 177 |

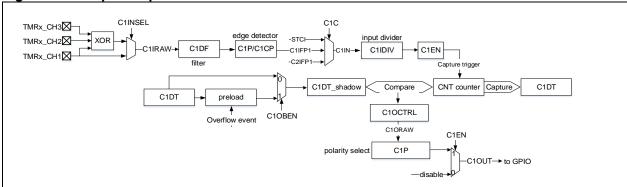

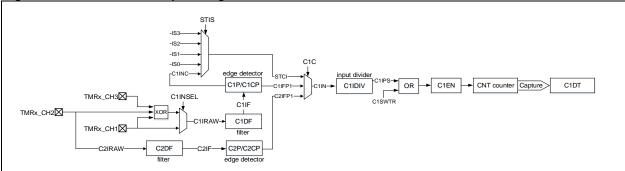

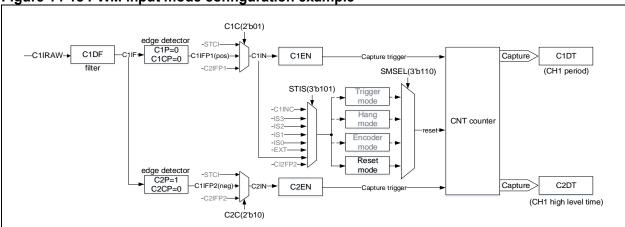

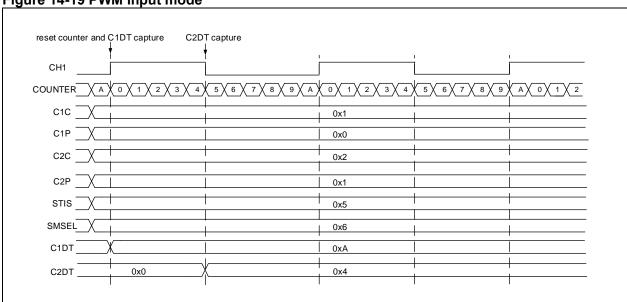

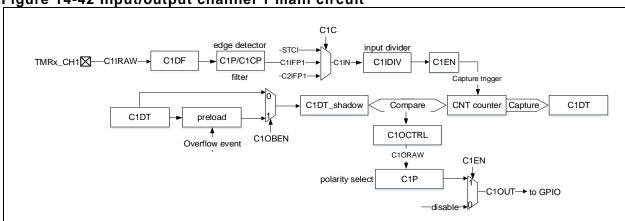

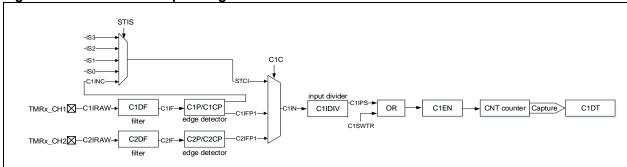

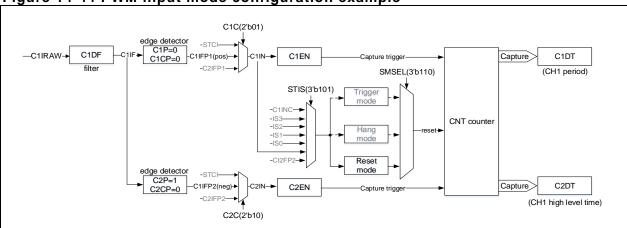

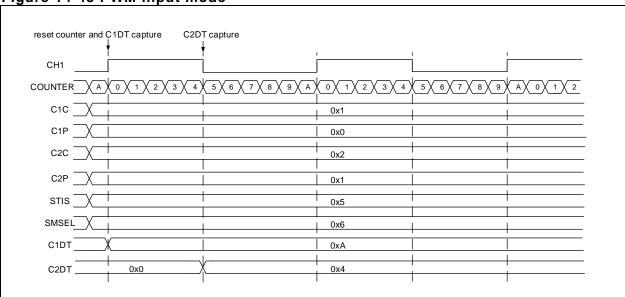

|    |       | 14.1.3.3 TMR input function              |     |

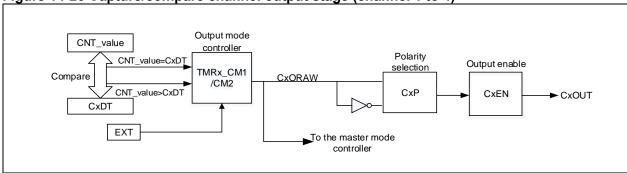

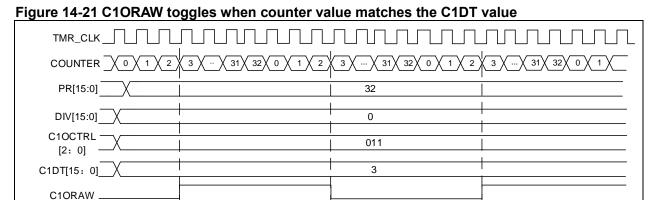

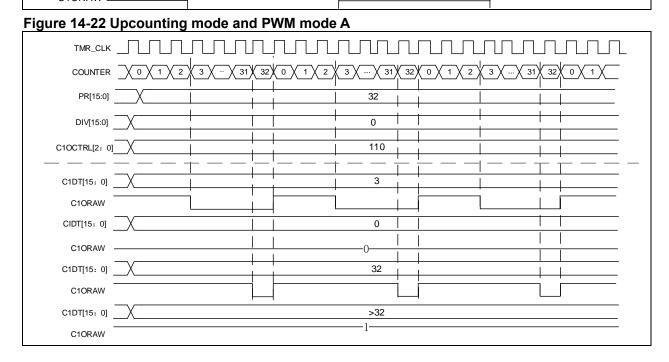

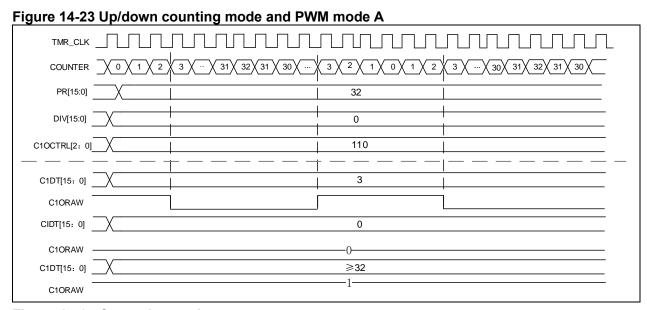

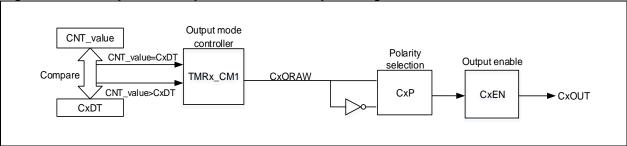

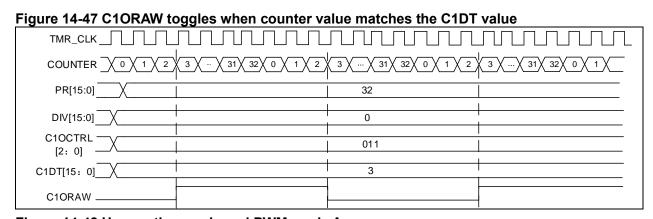

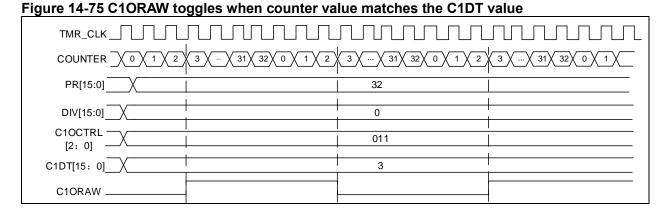

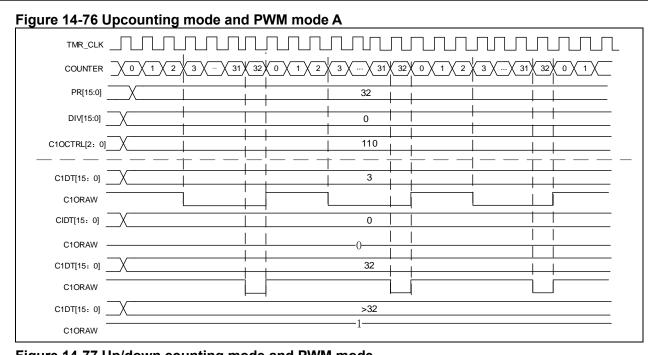

|    |       | 14.1.3.4 TMR output function             |     |

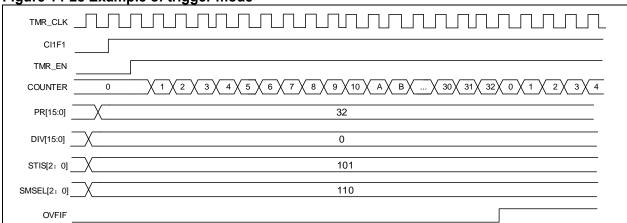

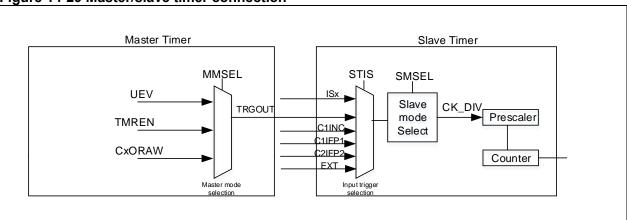

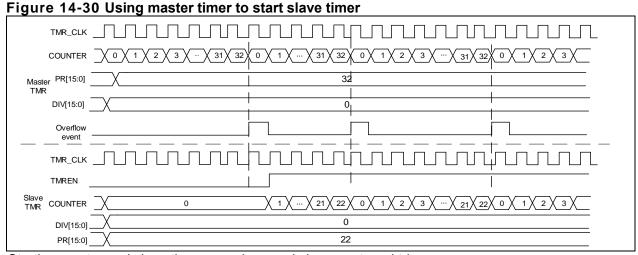

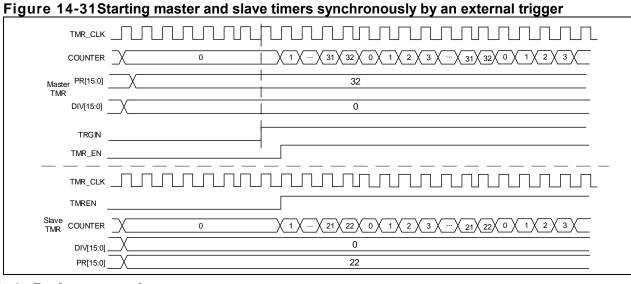

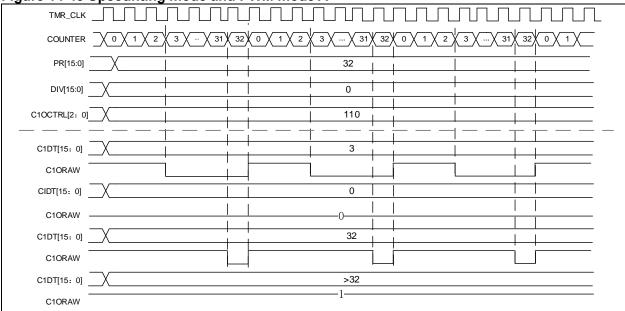

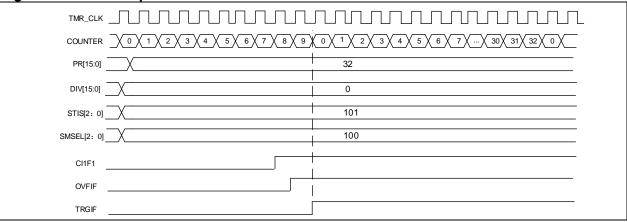

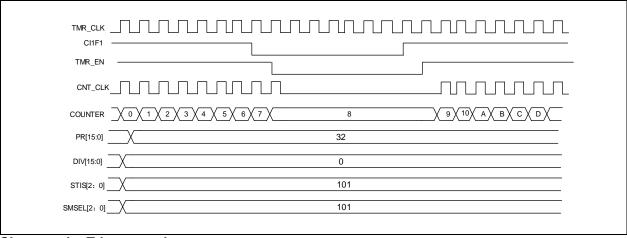

|    |       | 14.1.3.5 TMR synchronization             |     |

|    |       | 14.1.3.6 Debug mode                      | 188 |

|      | 14.1.4 TMRx reg                                                                                                                                                                                                                 | jisters                                                                                                                                                                                                                                                                                                               | 188                             |  |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|--|

|      | 14.1.4.1 C                                                                                                                                                                                                                      | ontrol register1 (TMRx_CTRL1)                                                                                                                                                                                                                                                                                         | 189                             |  |  |

|      | 14.1.4.2 C                                                                                                                                                                                                                      | ontrol register2 (TMRx_CTRL2)                                                                                                                                                                                                                                                                                         | 190                             |  |  |

|      | 14.1.4.3 S                                                                                                                                                                                                                      | lave timer control register (TMRx_STCTRL)                                                                                                                                                                                                                                                                             | 190                             |  |  |

|      | 14.1.4.4 D                                                                                                                                                                                                                      | 14.1.4.4 DMA/interrupt enable register (TMRx_IDEN)                                                                                                                                                                                                                                                                    |                                 |  |  |

|      | 14.1.4.5 In                                                                                                                                                                                                                     | nterrupt status register (TMRx_ISTS)                                                                                                                                                                                                                                                                                  | 192                             |  |  |

|      | 14.1.4.6 S                                                                                                                                                                                                                      | oftware event register (TMRx_SWEVT)                                                                                                                                                                                                                                                                                   | 194                             |  |  |

|      | 14.1.4.7 C                                                                                                                                                                                                                      | hannel mode register1 (TMRx_CM1)                                                                                                                                                                                                                                                                                      | 194                             |  |  |

|      | 14.1.4.8 C                                                                                                                                                                                                                      | hannel mode register2 (TMRx_CM2)                                                                                                                                                                                                                                                                                      | 196                             |  |  |

|      | 14.1.4.9 C                                                                                                                                                                                                                      | hannel control register (TMRx_CCTRL)                                                                                                                                                                                                                                                                                  | 197                             |  |  |

|      | 14.1.4.10                                                                                                                                                                                                                       | Counter value (TMRx_CVAL)                                                                                                                                                                                                                                                                                             | 198                             |  |  |

|      | 14.1.4.11                                                                                                                                                                                                                       | Division value (TMRx_DIV)                                                                                                                                                                                                                                                                                             | 198                             |  |  |

|      | 14.1.4.12                                                                                                                                                                                                                       | Period register (TMRx_PR)                                                                                                                                                                                                                                                                                             | 198                             |  |  |

|      | 14.1.4.13                                                                                                                                                                                                                       | Channel 1 data register (TMRx_C1DT)                                                                                                                                                                                                                                                                                   | 198                             |  |  |

|      | 14.1.4.14                                                                                                                                                                                                                       | Channel 2 data register (TMRx_C2DT)                                                                                                                                                                                                                                                                                   | 198                             |  |  |

|      | 14.1.4.15                                                                                                                                                                                                                       | Channel 3 data register (TMRx_C3DT)                                                                                                                                                                                                                                                                                   | 199                             |  |  |

|      | 14.1.4.16                                                                                                                                                                                                                       | Channel 4 data register (TMRx_C4DT)                                                                                                                                                                                                                                                                                   | 199                             |  |  |

|      | 14.1.4.17                                                                                                                                                                                                                       | DMA control register (TMRx_DMACTRL)                                                                                                                                                                                                                                                                                   | 199                             |  |  |

|      | 14.1.4.18                                                                                                                                                                                                                       | DMA data register (TMRx_DMADT)                                                                                                                                                                                                                                                                                        | 199                             |  |  |

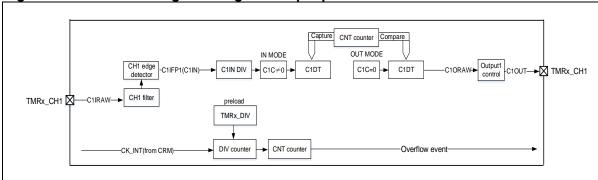

| 14.2 | General-purpos                                                                                                                                                                                                                  | se timer (TMR9 to TMR11)                                                                                                                                                                                                                                                                                              | 200                             |  |  |

|      | 14.2.1 TMRx intr                                                                                                                                                                                                                | roduction                                                                                                                                                                                                                                                                                                             | 200                             |  |  |

|      | 14 2 2 TMRx ma                                                                                                                                                                                                                  | in features                                                                                                                                                                                                                                                                                                           |                                 |  |  |

|      | <u></u>                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                       | 200                             |  |  |

|      |                                                                                                                                                                                                                                 | MR9 main features                                                                                                                                                                                                                                                                                                     |                                 |  |  |

|      | 14.2.2.1 T                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                       | 200                             |  |  |

|      | 14.2.2.1 TI<br>14.2.2.2 TI                                                                                                                                                                                                      | MR9 main features                                                                                                                                                                                                                                                                                                     | 200                             |  |  |

|      | 14.2.2.1 TI<br>14.2.2.2 TI<br>14.2.3 TMRx fun                                                                                                                                                                                   | MR9 main features MR10 and TMR11 main features                                                                                                                                                                                                                                                                        | 200<br>200<br>201               |  |  |

|      | 14.2.2.1 TI<br>14.2.2.2 TI<br>14.2.3 TMRx fun<br>14.2.3.1 C                                                                                                                                                                     | MR9 main features MR10 and TMR11 main features ctional overview                                                                                                                                                                                                                                                       | 200<br>200<br>201               |  |  |

|      | 14.2.2.1 TI<br>14.2.2.2 TI<br>14.2.3 TMRx fun<br>14.2.3.1 C<br>14.2.3.2 C                                                                                                                                                       | MR9 main features MR10 and TMR11 main features ctional overview ounting clock                                                                                                                                                                                                                                         | 200<br>200<br>201<br>201        |  |  |

|      | 14.2.2.1 TI<br>14.2.2.2 TI<br>14.2.3 TMRx fun<br>14.2.3.1 C<br>14.2.3.2 C<br>14.2.3.3 TI                                                                                                                                        | MR9 main features  MR10 and TMR11 main features  ctional overview  ounting clock  ounting mode                                                                                                                                                                                                                        | 200<br>201<br>201<br>203        |  |  |

|      | 14.2.2.1 TI<br>14.2.2.2 TI<br>14.2.3 TMRx fun<br>14.2.3.1 C<br>14.2.3.2 C<br>14.2.3.3 TI<br>14.2.3.4 TI                                                                                                                         | MR9 main features  MR10 and TMR11 main features  ctional overview  ounting clock  ounting mode  MR input function                                                                                                                                                                                                     | 200<br>201<br>201<br>203<br>204 |  |  |

|      | 14.2.2.1 TI<br>14.2.2.2 TI<br>14.2.3 TMRx fun<br>14.2.3.1 C<br>14.2.3.2 C<br>14.2.3.3 TI<br>14.2.3.4 TI<br>14.2.3.5 TI                                                                                                          | MR9 main features  MR10 and TMR11 main features  ctional overview  ounting clock  ounting mode  MR input function  MR output function                                                                                                                                                                                 | 200201201203204206              |  |  |

|      | 14.2.2.1 TI<br>14.2.2.2 TI<br>14.2.3 TMRx fun<br>14.2.3.1 C<br>14.2.3.2 C<br>14.2.3.3 TI<br>14.2.3.4 TI<br>14.2.3.5 TI<br>14.2.3.6 D                                                                                            | MR9 main features  MR10 and TMR11 main features  ounting clock  ounting mode  MR input function  MR output function  MR synchronization                                                                                                                                                                               |                                 |  |  |

|      | 14.2.2.1 TI<br>14.2.2.2 TI<br>14.2.3 TMRx fun<br>14.2.3.1 C<br>14.2.3.2 C<br>14.2.3.3 TI<br>14.2.3.4 TI<br>14.2.3.5 TI<br>14.2.3.6 D<br>14.2.4 TMR9 reg                                                                         | MR9 main features  MR10 and TMR11 main features  ctional overview  ounting clock  ounting mode  MR input function  MR output function  MR synchronization  ebug mode                                                                                                                                                  |                                 |  |  |

|      | 14.2.2.1 TI<br>14.2.2.2 TI<br>14.2.3 TMRx fun<br>14.2.3.1 C<br>14.2.3.2 C<br>14.2.3.3 TI<br>14.2.3.4 TI<br>14.2.3.5 TI<br>14.2.3.6 D<br>14.2.4 TMR9 reg<br>14.2.4.1 C                                                           | MR9 main features  MR10 and TMR11 main features  ounting clock  ounting mode  MR input function  MR output function  MR synchronization  ebug mode  gisters                                                                                                                                                           |                                 |  |  |

|      | 14.2.2.1 TI<br>14.2.2.2 TI<br>14.2.3 TMRx fun<br>14.2.3.1 C<br>14.2.3.2 C<br>14.2.3.3 TI<br>14.2.3.4 TI<br>14.2.3.5 TI<br>14.2.3.6 D<br>14.2.4 TMR9 reg<br>14.2.4.1 C<br>14.2.4.2 S                                             | MR9 main features  MR10 and TMR11 main features  ctional overview  ounting clock  ounting mode  MR input function  MR output function  MR synchronization  ebug mode  gisters  ontrol register1 (TMR9_CTRL1)                                                                                                          |                                 |  |  |

|      | 14.2.2.1 TI<br>14.2.2.2 TI<br>14.2.3 TMRx fun<br>14.2.3.1 C<br>14.2.3.2 C<br>14.2.3.3 TI<br>14.2.3.4 TI<br>14.2.3.5 TI<br>14.2.3.6 D<br>14.2.4 TMR9 reg<br>14.2.4.1 C<br>14.2.4.2 S<br>14.2.4.3 D                               | MR9 main features  MR10 and TMR11 main features  ctional overview  ounting clock  ounting mode  MR input function  MR output function  MR synchronization  ebug mode  gisters  ontrol register1 (TMR9_CTRL1)                                                                                                          |                                 |  |  |

|      | 14.2.2.1 TI<br>14.2.2.2 TI<br>14.2.3 TMRx fun<br>14.2.3.1 C<br>14.2.3.2 C<br>14.2.3.3 TI<br>14.2.3.4 TI<br>14.2.3.5 TI<br>14.2.3.6 D<br>14.2.4 TMR9 reg<br>14.2.4.1 C<br>14.2.4.2 SI<br>14.2.4.3 D<br>14.2.4.4 In               | MR9 main features  MR10 and TMR11 main features  ctional overview  ounting clock  ounting mode  MR input function  MR output function  MR synchronization  ebug mode  gisters  ontrol register1 (TMR9_CTRL1)  lave timer control register (TMR9_IDEN)                                                                 |                                 |  |  |

|      | 14.2.2.1 TI<br>14.2.2.2 TI<br>14.2.3 TMRx fun<br>14.2.3.1 C<br>14.2.3.2 C<br>14.2.3.3 TI<br>14.2.3.4 TI<br>14.2.3.5 TI<br>14.2.3.6 D<br>14.2.4 TMR9 reg<br>14.2.4.1 C<br>14.2.4.2 S<br>14.2.4.3 D<br>14.2.4.4 In<br>14.2.4.5 Sc | MR9 main features  MR10 and TMR11 main features  Outling olock  Ounting mode  MR input function  MR output function  MR synchronization  ebug mode  gisters  Ontrol register1 (TMR9_CTRL1)  lave timer control register (TMR9_STCTRL)  MA/interrupt enable register (TMR9_IDEN)  oterrupt status register (TMR9_ISTS) |                                 |  |  |

|      | 14.2.4.7 Channel control register (TMR9_CCTRL)           | 215   |

|------|----------------------------------------------------------|-------|

|      | 14.2.4.8 Counter value (TMR9_CVAL)                       | 216   |

|      | 14.2.4.9 Division value (TMR9_DIV)                       | 216   |

|      | 14.2.4.10 Period register (TMR9_PR)                      | 216   |

|      | 14.2.4.11 Channel 1 data register (TMR9_C1DT)            | 216   |

|      | 14.2.4.12 Channel 2 data register (TMR9_C2DT)            | 217   |

|      | 14.2.5 TMR10 and TMR11 registers                         | 217   |

|      | 14.2.5.1 Control register1 (TMRx_CTRL1)                  | 217   |

|      | 14.2.5.2 DMA/interrupt enable register (TMRx_IDEN)       | 218   |

|      | 14.2.5.3 Interrupt status register (TMRx_ISTS)           | 218   |

|      | 14.2.5.4 Software event register (TMRx_SWEVT)            | 218   |

|      | 14.2.5.5 Channel mode register1 (TMRx_CM1)               | 220   |

|      | 14.2.5.6 Channel control register (TMRx_CCTRL)           | 221   |

|      | 14.2.5.7 Counter value (TMRx_CVAL)                       | 222   |

|      | 14.2.5.8 Division value (TMRx_DIV)                       | 222   |

|      | 14.2.5.9 Period register (TMRx_PR)                       | 222   |

|      | 14.2.5.10 Channel 1 data register (TMRx_C1DT)            | 222   |

| 14.3 | Advanced-control timers (TMR1)                           | . 223 |

|      | 14.3.1 TMR1 introduction                                 | 223   |

|      | 14.3.2 TMR1 main features                                | 223   |

|      | 14.3.3 TMR1 functional overview                          | 224   |

|      | 14.3.3.1 Counting clock                                  | 224   |

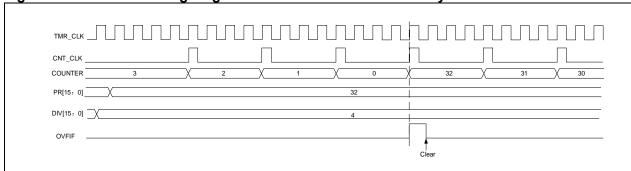

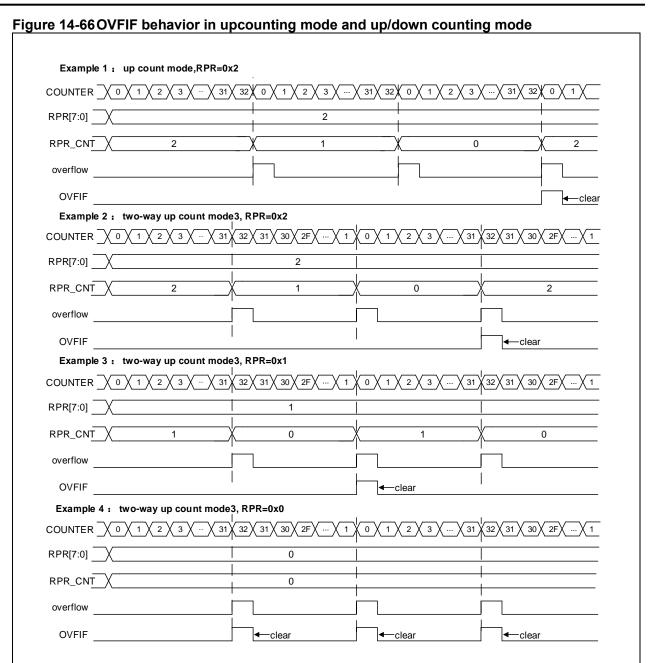

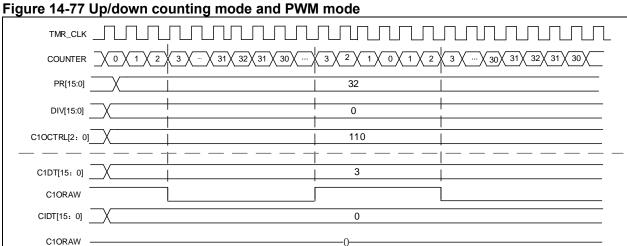

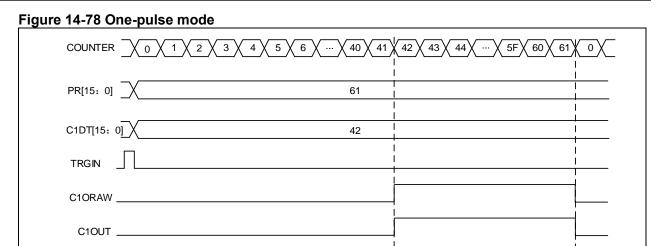

|      | 14.3.3.2 Counting mode                                   | 227   |

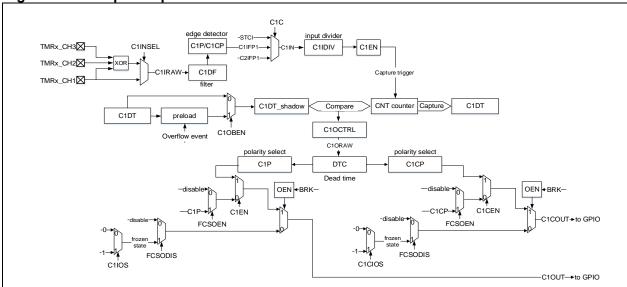

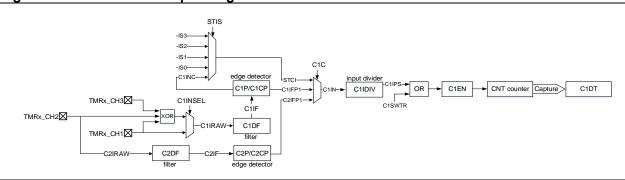

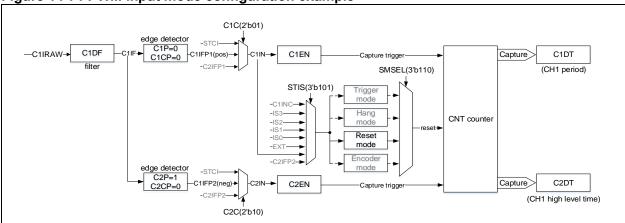

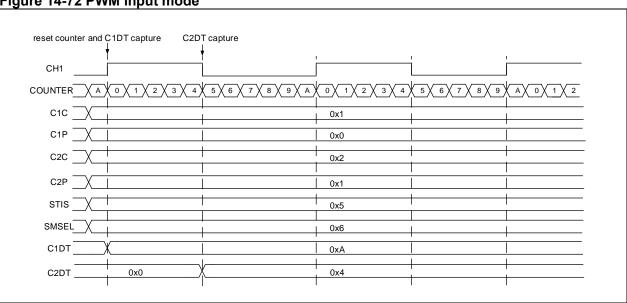

|      | 14.3.3.3 TMR input function                              | 232   |

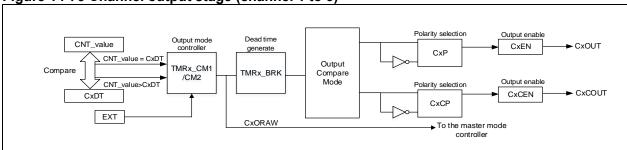

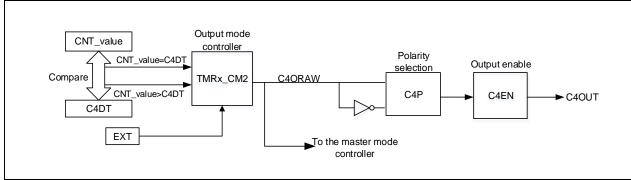

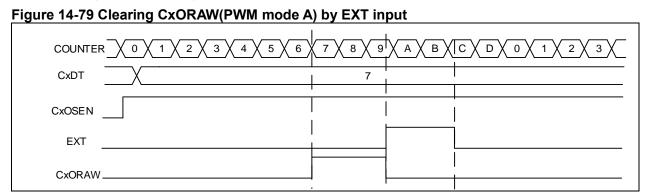

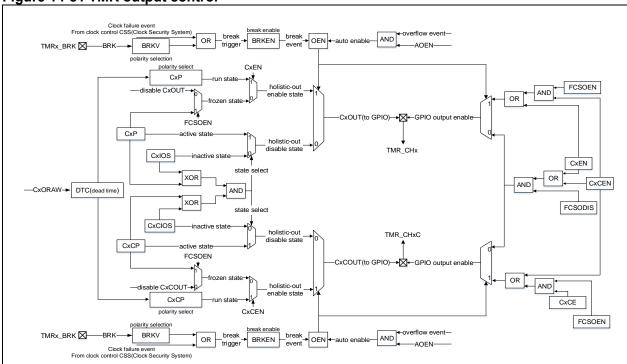

|      | 14.3.3.4 TMR output function                             | 235   |

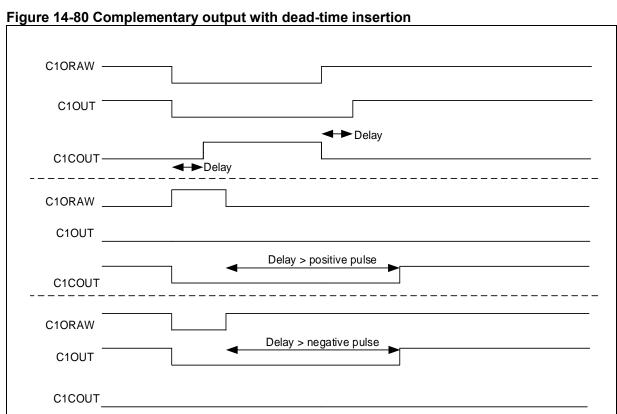

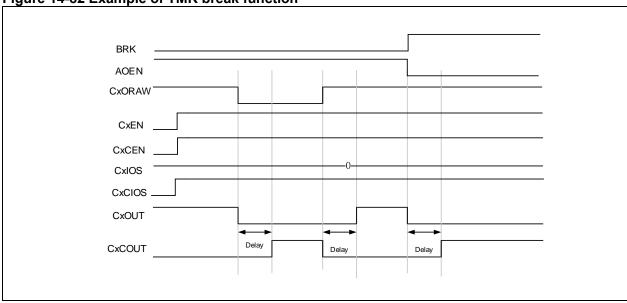

|      | 14.3.3.5 TMR break function                              | 239   |

|      | 14.3.3.6 TMR synchronization                             | 241   |

|      | 14.3.3.7 Debug mode                                      | 242   |

|      | 14.3.4 TMR1 registers                                    | 242   |

|      | 14.3.4.1 TMR1 control register1 (TMR1_CTRL1)             | 242   |

|      | 14.3.4.2 TMR1 control register2 (TMR1_CTRL2)             | 243   |

|      | 14.3.4.3 TMR1 slave timer control register (TMR1_STCTRL) | 244   |

|      | 14.3.4.4 TMR1 DMA/interrupt enable register (TMR1_IDEN)  | 245   |

|      | 14.3.4.5 TMR1 interrupt status register (TMR1_ISTS)      | 246   |

|      | 14.3.4.6 TMR1 software event register (TMR1_SWEVT)       | 248   |

|      | 14.3.4.7 TMR1 channel mode register1 (TMR1_CM1)          | 248   |

|      | 14.3.4.8 TMR1 channel mode register2 (TMR1_CM2)          | 250   |

|      | 14.3.4.9 TMR1 Channel control register (TMR1_CCTRL)      | 251   |

|      |                                                          |       |

|    |      | 14.3.4.10          | TMR1 counter value (TMR1_CVAL)             | 253 |

|----|------|--------------------|--------------------------------------------|-----|

|    |      | 14.3.4.11          | TMR1 division value (TMR1_DIV)             | 253 |

|    |      | 14.3.4.12          | TMR1 period register (TMR1_PR)             | 253 |

|    |      | 14.3.4.13          | TMR1 repetition period register (TMR1_RPR) | 253 |

|    |      | 14.3.4.14          | TMR1 channel 1 data register (TMR1_C1DT)   | 253 |

|    |      | 14.3.4.15          | TMR1 channel 2 data register (TMR1_C2DT)   | 253 |

|    |      |                    | TMR1 channel 3 data register (TMR1_C3DT)   |     |

|    |      |                    | TMR1 channel 4 data register (TMRx_C4DT)   |     |

|    |      |                    | TMR1 break register (TMR1_BRK)             |     |

|    |      |                    | TMR1 DMA control register (TMR1_DMACTRL)   |     |

|    |      | 14.3.4.20          | TMR1 DMA data register (TMR1_DMADT)        | 255 |

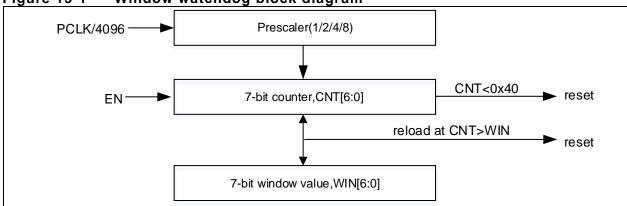

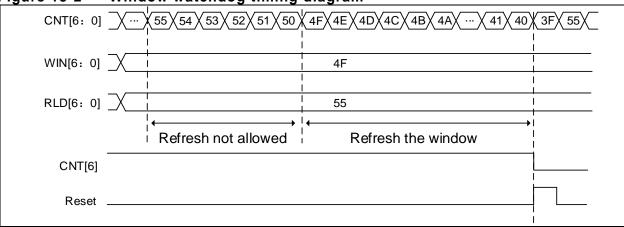

| 15 | Wind | ow watchdog t      | imer (WWDT)                                | 256 |

|    | 15.1 | WWDT introduct     | tion                                       | 256 |

|    | 15.2 | WWDT main fea      | tures                                      | 256 |

|    | 15.3 | WWDT functions     | al overview                                | 256 |

|    | 15.4 | Debug mode         |                                            | 257 |

|    | 15.5 | WWDT registers     | ·                                          | 257 |

|    |      | 15.5.1 Control reg | gister (WWDT_CTRL)                         | 257 |

|    |      |                    | ion register (WWDT_CFG)                    |     |

|    |      | 15.5.3 Status reg  | ister (WWDT_STS)                           | 258 |

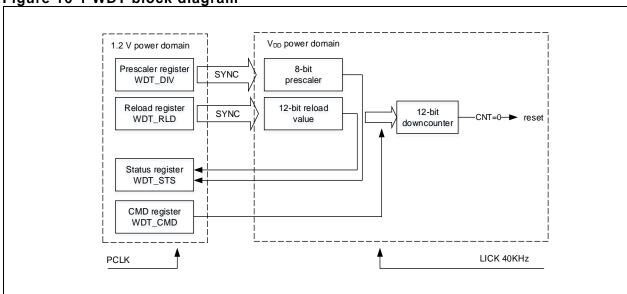

| 16 | Watc | hdog timer (WI     | ЭТ)                                        | 259 |

|    | 16.1 | WDT introduction   | n                                          | 259 |

|    | 16.2 | WDT main featu     | res                                        | 259 |

|    | 16.3 | WDT functional     | overview                                   | 259 |

|    | 16.4 | Debug mode         |                                            | 260 |

|    | 16.5 | WDT registers      |                                            | 260 |

|    |      | 16.5.1 Command     | register (WDT_CMD)                         | 260 |

|    |      | 16.5.2 Divider reg | gister (WDT_DIV)                           | 260 |

|    |      | 16.5.3 Reload reg  | gister (WDT_RLD)                           | 261 |

|    |      | _                  | ister (WDT_STS)                            |     |

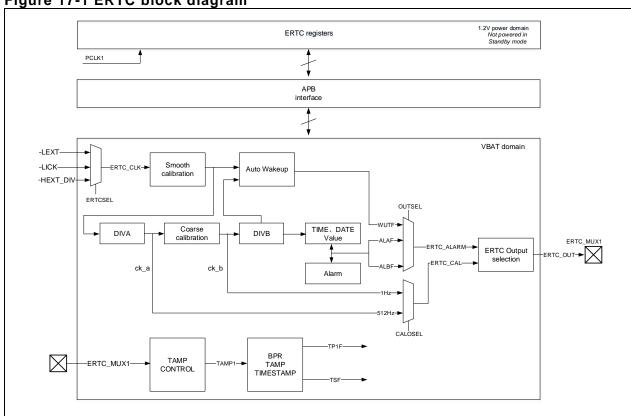

| 17 | Enha | nced real-time     | clock (ERTC)                               | 262 |

|    | 17.1 | ERTC introducti    | on                                         | 262 |

|    | 17.2 | ERTC main feat     | ures                                       | 262 |

| 17.3  | ERTC function overview                                        | 263 |

|-------|---------------------------------------------------------------|-----|

|       | 17.3.1 ERTC clock                                             | 263 |

|       | 17.3.2 ERTC initialization                                    | 263 |

|       | 17.3.3 Periodic automatic wakeup                              | 265 |

|       | 17.3.4 ERTC calibration                                       | 265 |

|       | 17.3.5 Reference clock detection                              | 266 |

|       | 17.3.6 Time stamp                                             | 266 |

|       | 17.3.7 Tamper detection                                       | 267 |

|       | 17.3.8 Multiplexed function output                            | 267 |

|       | 17.3.9 ERTC wakeup                                            | 268 |

| 17.4  | ERTC registers                                                | 268 |

|       | 17.4.1 ERTC time register (ERTC_TIME)                         | 269 |

|       | 17.4.2 ERTC date register (ERTC_DATE)                         | 269 |

|       | 17.4.3 ERTC control register (ERTC_CTRL)                      | 271 |

|       | 17.4.4 ERTC initialization and status register (ERTC_STS)     | 272 |

|       | 17.4.5 ERTC divider register (ERTC_DIV)                       | 273 |

|       | 17.4.6 ERTC wakeup timer register (ERTC_WAT)                  | 273 |

|       | 17.4.7 ERTC coarse calibration register (ERTC_CCAL)           | 274 |

|       | 17.4.8 ERTC alarm clock A register (ERTC_ALA)                 | 274 |

|       | 17.4.9 ERTC alarm clock B register (ERTC_ALB)                 | 275 |

|       | 17.4.10 ERTC write protection register (ERTC_WP)              | 275 |

|       | 17.4.11 ERTC subsecond register (ERTC_SBS)                    | 275 |

|       | 17.4.12 ERTC time adjustment register (ERTC_TADJ)             | 275 |

|       | 17.4.13 ERTC time stamp time register (ERTC_TSTM)             | 276 |

|       | 17.4.14 ERTC time stamp date register (ERTC_TSDT)             | 276 |

|       | 17.4.15 ERTC time stamp subsecond register (ERTC_TSSBS)       | 276 |

|       | 17.4.16 ERTC smooth calibration register (ERTC_SCAL)          | 276 |

|       | 17.4.17 ERTC tamper configuration register (ERTC_TAMP)        | 277 |

|       | 17.4.18 ERTC alarm clock A subsecond register (ERTC_ALASBS)   | 278 |

|       | 17.4.19 ERTC alarm clock B subsecond register (ERTC_ALBSBS)   | 278 |

|       | 17.4.20 ERTC battery powered domain data register (ERTC_BPRx) | 278 |

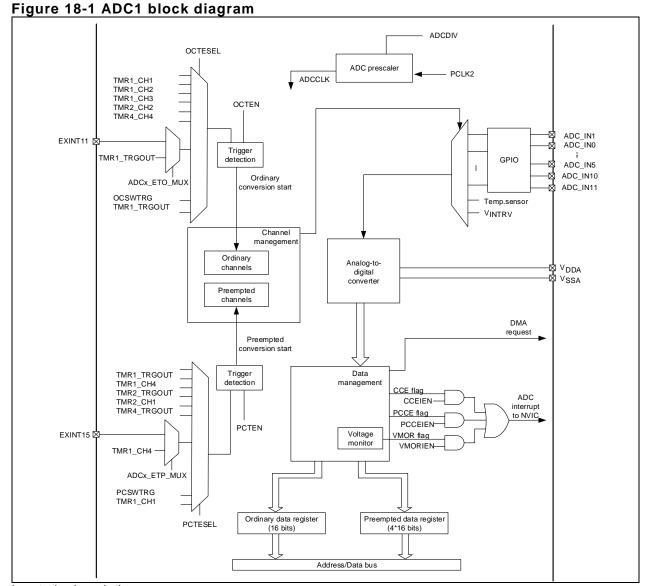

| Analo | og-to-digital converter (ADC)                                 | 279 |

| 18.1  | ADC introduction                                              | 279 |

| 18.2  | ADC main features                                             | 279 |

|       |                                                               |     |

18

| 18.3 | ADC structure                                                 | . 279 |

|------|---------------------------------------------------------------|-------|

| 18.4 | ADC functional overview                                       | . 280 |

|      | 18.4.1 Channel management                                     | 280   |

|      | 18.4.1.1 Internal temperature sensor                          | 281   |

|      | 18.4.1.2 Internal reference voltage                           | 281   |

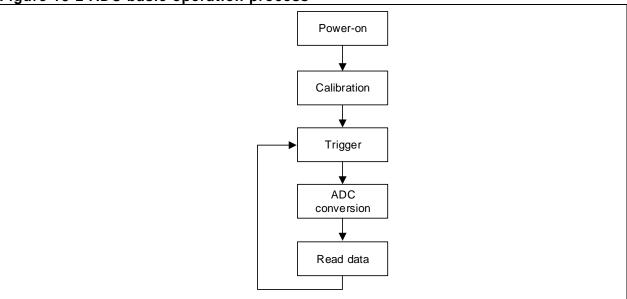

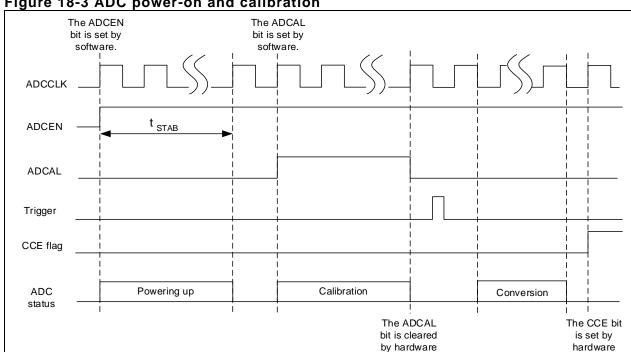

|      | 18.4.2 ADC operation process                                  | 281   |

|      | 18.4.2.1 Power-on and calibration                             | 281   |

|      | 18.4.2.2 Trigger                                              | 282   |

|      | 18.4.2.3 Sampling and conversion sequence                     | 283   |

|      | 18.4.3 Conversion sequence management                         | 283   |

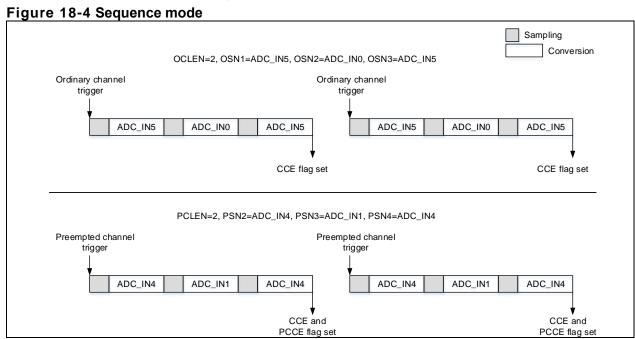

|      | 18.4.3.1 Sequence mode                                        | 283   |

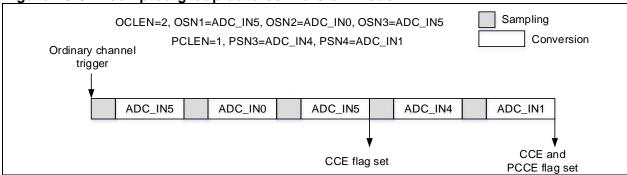

|      | 18.4.3.2 Automatic preempted group conversion mode            | 284   |

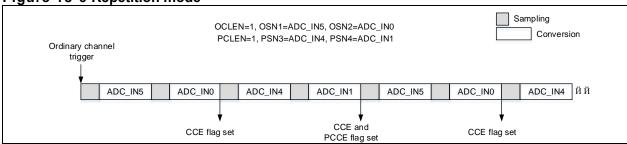

|      | 18.4.3.3 Repetition mode                                      |       |

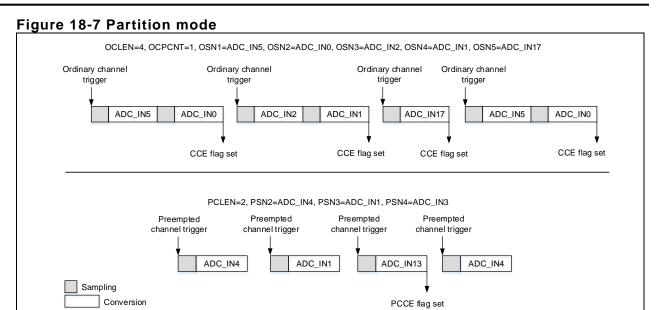

|      | 18.4.3.4 Partition mode                                       | 284   |

|      | 18.4.4 Data management                                        | 285   |

|      | 18.4.4.1 Data alignment                                       |       |

|      | 18.4.4.2 Data read                                            |       |

|      | 18.4.5 Voltage monitoring                                     | 286   |

|      | 18.4.6 Status flag and interrupts                             |       |

| 18.5 | ADC registers                                                 | . 286 |

|      | 18.5.1 ADC status register (ADC_STS)                          | 287   |

|      | 18.5.2 ADC control register1 (ADC_CTRL1)                      | 287   |

|      | 18.5.3 ADC control register2 (ADC_CTRL2)                      | 288   |

|      | 18.5.4 ADC sampling time register 1 (ADC_SPT1)                | 290   |

|      | 18.5.5 ADC sampling time register 2 (ADC_SPT2)                | 291   |

|      | 18.5.6 ADC preempted channel data offset register x           |       |

|      | (ADC_ PCDTOx) (x=14)                                          | 292   |

|      | 18.5.7 ADC voltage monitor high threshold register (ADC_VWHB) | 292   |

|      | 18.5.8 ADC voltage monitor low threshold register (ADC_ VWLB) | 292   |

|      | 18.5.9 ADC ordinary sequence register 1 (ADC_ OSQ1)           | 292   |

|      | 18.5.10 ADC ordinary sequence register 2 (ADC_ OSQ2)          | 293   |

|      | 18.5.11 ADC ordinary sequence register 3 (ADC_ OSQ3)          |       |

|      | 18.5.12 ADC preempted sequence register (ADC_ PSQ)            |       |

|      | 18.5.13 ADC preempted data register x (ADC_ PDTx) (x=14)      |       |

|      | 18.5.14 ADC ordinary data register (ADC_ ODT)                 |       |

|      | reserve the standard data register (100_ 001)                 |       |

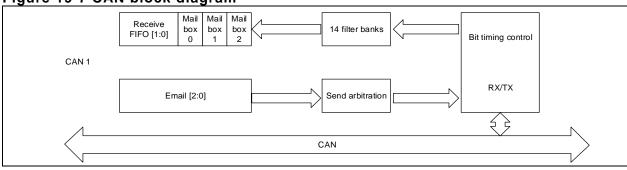

| 9 | Conti | roller area network (CAN)295                                            |

|---|-------|-------------------------------------------------------------------------|

|   | 19.1  | CAN introduction                                                        |

|   | 19.2  | CAN main features                                                       |

|   | 19.3  | Baud rate                                                               |

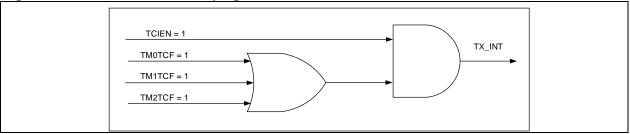

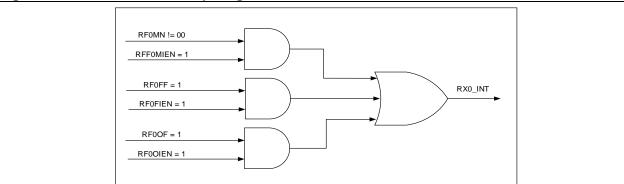

|   | 19.4  | Interrupt management                                                    |

|   | 19.5  | Design tips                                                             |

|   | 19.6  | Functional overview                                                     |

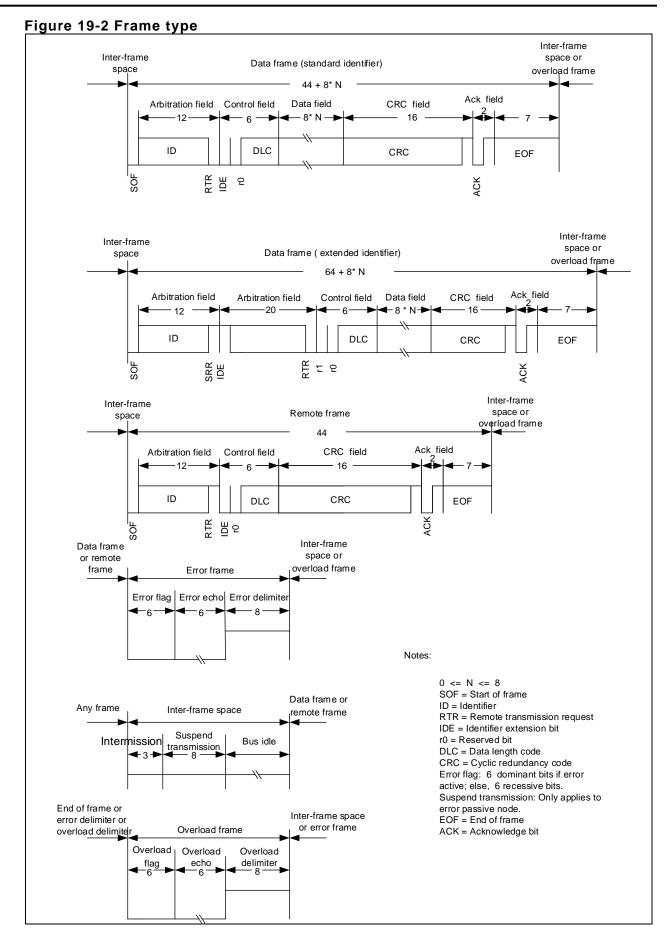

|   |       | 19.6.1 General description299                                           |

|   |       | 19.6.2 Operating modes                                                  |

|   |       | 19.6.3 Test modes                                                       |

|   |       | 19.6.4 Message filtering301                                             |

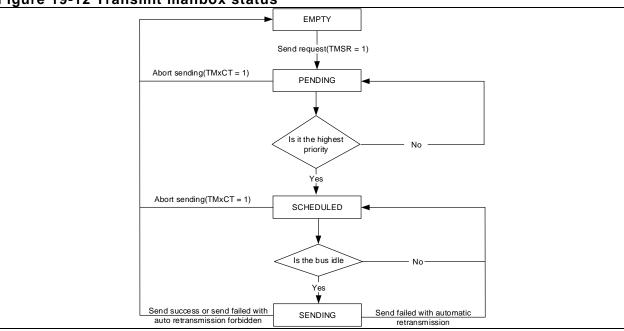

|   |       | 19.6.5 Message transmission                                             |

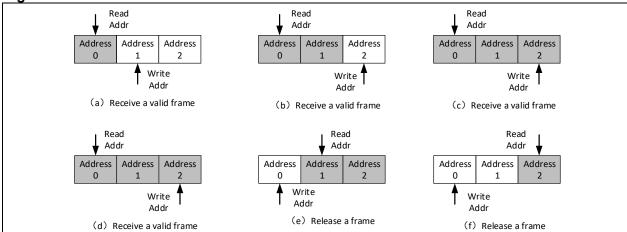

|   |       | 19.6.6 Message reception304                                             |

|   |       | 19.6.7 Error management305                                              |

|   | 19.7  | CAN registers                                                           |

|   |       | 19.7.1 CAN control and status registers307                              |

|   |       | 19.7.1.1 CAN master control register (CAN_MCTRL)                        |

|   |       | 19.7.1.2 CAN master status register (CAN_MSTS)                          |

|   |       | 19.7.1.3 CAN transmit status register (CAN_TSTS)                        |

|   |       | 19.7.1.4 CAN receive FIFO 0 register (CAN_RF0)                          |

|   |       | 19.7.1.5 CAN receive FIFO 1 register (CAN_RF1)                          |

|   |       | 19.7.1.6 CAN interrupt enable register (CAN_INTEN)                      |

|   |       | 19.7.1.7 CAN error status register (CAN_ESTS)                           |

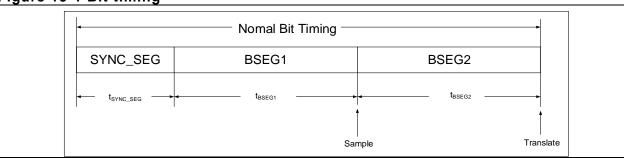

|   |       | 19.7.1.8 CAN bit timing register (CAN_BTMG)                             |

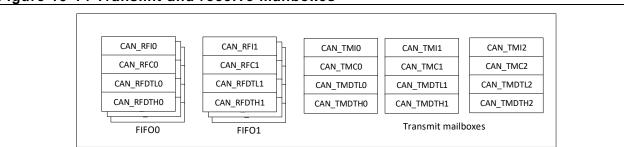

|   |       | 19.7.2 CAN mailbox registers315                                         |

|   |       | 19.7.2.1 Transmit mailbox identifier register (CAN_TMIx) (x=02) 316     |

|   |       | 19.7.2.2 Transmit mailbox data length and time stamp register           |

|   |       | (CAN_TMCx) (x=02)                                                       |

|   |       | 19.7.2.3 Transmit mailbox data low register (CAN_TMDTLx) (x=02) 316     |

|   |       | 19.7.2.4 Transmit mailbox data high register (CAN_TMDTHx) (x=02) 317    |

|   |       | 19.7.2.5 Receive FIFO mailbox identifier register (CAN_RFIx) (x=01) 317 |

|   |       | 19.7.2.6 Receive FIFO mailbox data length and time stamp register       |

|   |       | (CAN_RFCx) (x=01)                                                       |

|   |       | 19.7.2.7 Receive FIFO mailbox data low register (CAN_RFDTLx) (x=01)317  |

|   |       | 19.7.2.8 Receive FIFO mailbox data high register (CAN_RFDTHx) (x=01)318 |

|   |       | 19.7.3 CAN filter registers318                                          |

|    |       | 19.7.3.1 C      | AN filter control register (CAN_FCTRL)                         | 318    |

|----|-------|-----------------|----------------------------------------------------------------|--------|

|    |       | 19.7.3.2 C      | AN filter mode configuration register (CAN_FMCFG)              | 318    |

|    |       | 19.7.3.3 C      | AN filter bit width configuration register (CAN_ FBWCFG)       | 318    |

|    |       | 19.7.3.4 C      | AN filter FIFO association register (CAN_ FRF)                 | 318    |

|    |       | 19.7.3.5 C      | AN filter activation control register (CAN_ FACFG)             | 319    |

|    |       | 19.7.3.6 C      | AN filter bank i filter bit register (CAN_ FiFBx) (i=013; x=1. | .2)319 |

| 20 | Unive | rsal serial bu  | s full-seed device interface (OTGFS)                           | 320    |

|    | 20.1  | USBFS structu   | ·e                                                             | . 320  |

|    | 20.2  | OTGFS functio   | nal description                                                | . 320  |

|    | 20.3  | OTGFS clock a   | nd pin configuration                                           | . 321  |

|    |       | 20.3.1 OTGFS cl | ock configuration                                              | 321    |

|    |       | 20.3.2 OTGFS p  | n configuration                                                | 321    |

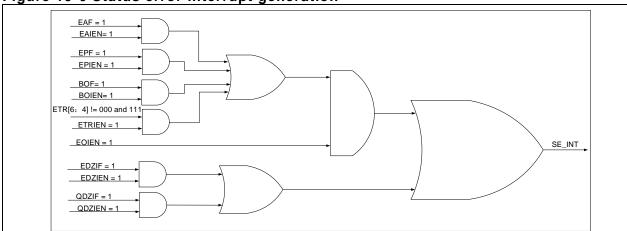

|    | 20.4  | OTGFS interrup  | ots                                                            | . 321  |

|    | 20.5  | OTGFS functio   | nal description                                                | . 322  |

|    |       | 20.5.1 OTGFS in | itialization                                                   | 322    |

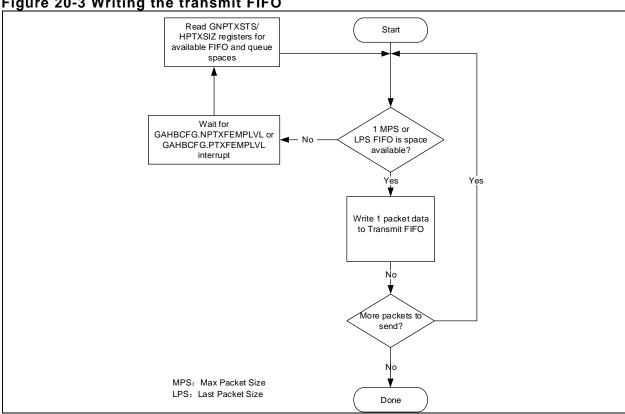

|    |       | 20.5.2 OTGFS F  | IFO configuration                                              | 323    |

|    |       | 20.5.2.1 D      | evice mode                                                     | 323    |

|    |       | 20.5.2.2 H      | ost mode                                                       | 324    |

|    |       | 20.5.2.3 R      | efresh controller transmit FIFO                                | 325    |

|    |       | 20.5.3 OTGFS h  | ost mode                                                       | 325    |

|    |       | 20.5.3.1 H      | ost initialization                                             | 325    |

|    |       | 20.5.3.2 O      | TGFS channel initialization                                    | 326    |

|    |       | 20.5.3.3 H      | alting a channel                                               | 326    |

|    |       | 20.5.3.4 Q      | ueue depth                                                     | 326    |

|    |       | 20.5.3.5 S      | pecial cases                                                   | 328    |

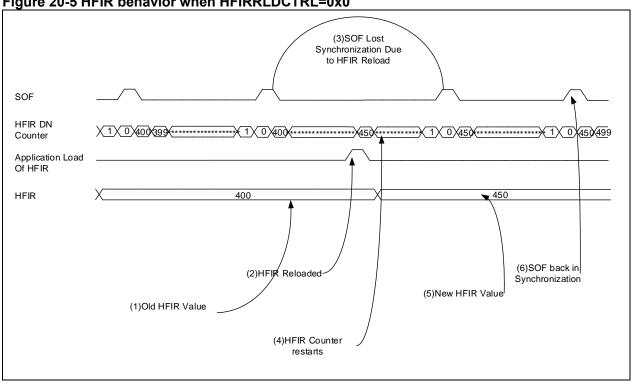

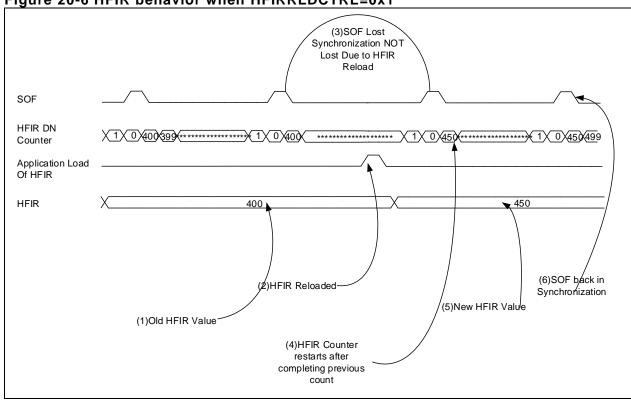

|    |       | 20.5.3.6 H      | ost HFIR feature                                               | 328    |

|    |       | 20.5.3.7 In     | itialize bulk and control IN transfers                         | 329    |

|    |       | 20.5.3.8 In     | itialize bulk and control OUT/SETUP transfers                  | 331    |

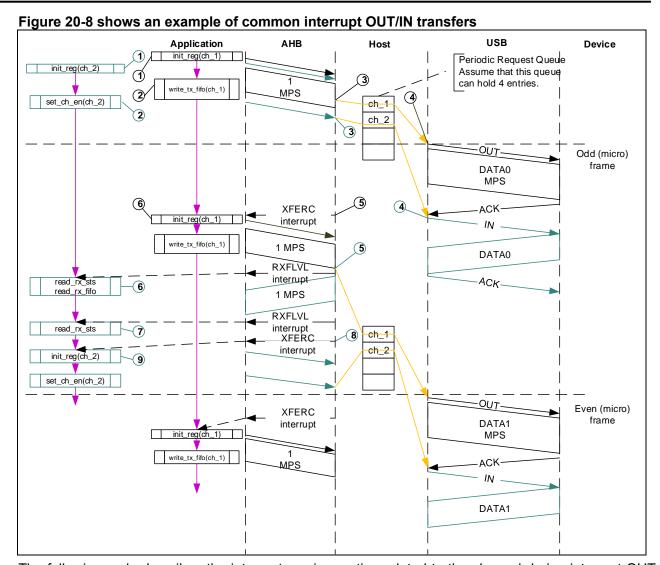

|    |       | 20.5.3.9 In     | itialize interrupt IN transfers                                | 333    |

|    |       | 20.5.3.10       | Initialize interrupt OUT transfers                             | 335    |

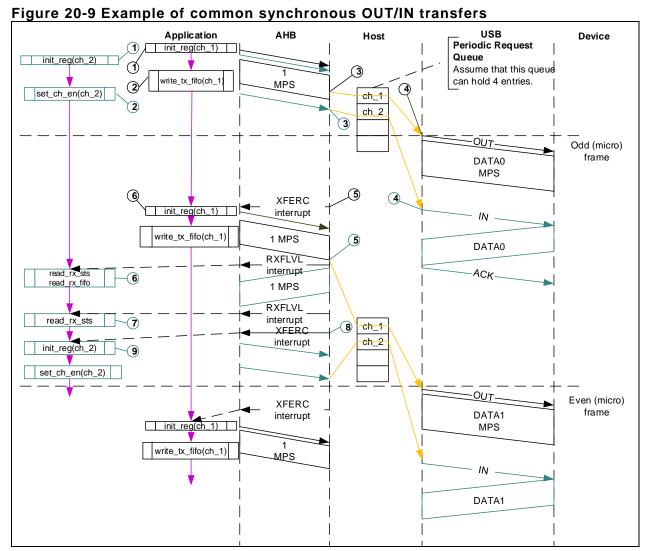

|    |       | 20.5.3.11       | Initialize synchronous IN transfers                            | 337    |

|    |       | 20.5.3.12       | Initialize synchronous OUT transfers                           | 338    |

|    |       | 20.5.4 OTGFS d  | evice mode                                                     | 340    |

|    |       | 20.5.4.1 D      | evice initialization                                           | 340    |

|    |       | 20.5.4.2 E      | ndpoint initialization on USB reset                            | 340    |

|    |       | 20.5.4.3 E      | ndpoint initialization on enumeration completion               | 341    |

|      | 20.5.4.4 E       | ndpoint initialization on SetAddress command                 | 341       |

|------|------------------|--------------------------------------------------------------|-----------|

|      | 20.5.4.5 E       | ndpoint initialization on SetConfiguration/SetInterface comm | and341    |

|      | 20.5.4.6 E       | ndpoint activation                                           | 341       |

|      | 20.5.4.7 U       | SB endpoint deactivation                                     | 342       |

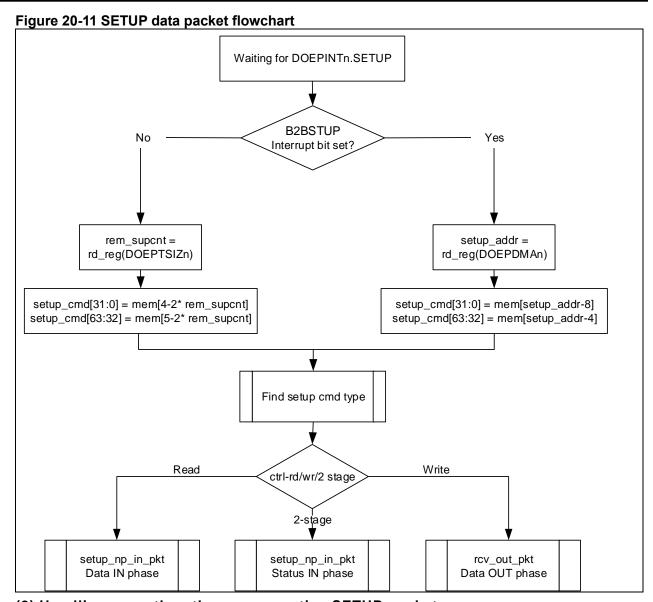

|      | 20.5.4.8 C       | ontrol write transfers (SETUP/Data OUT/Status IN)            | 342       |

|      | 20.5.4.9 C       | ontrol read transfers (SETUP/Data IN/Status OUT)             | 342       |

|      | 20.5.4.10        | Control transfers (SETUP/Status IN)                          | 343       |

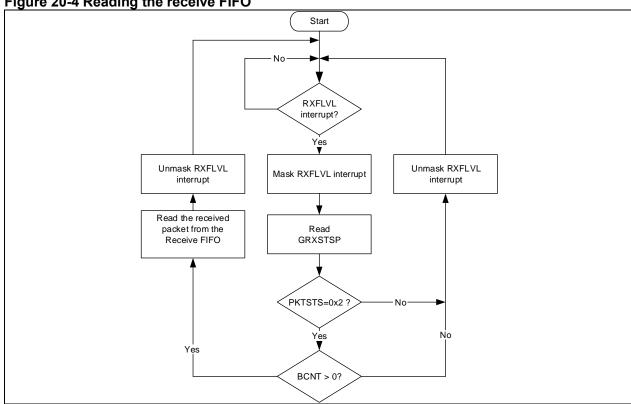

|      | 20.5.4.11        | Read FIFO packets                                            | 343       |

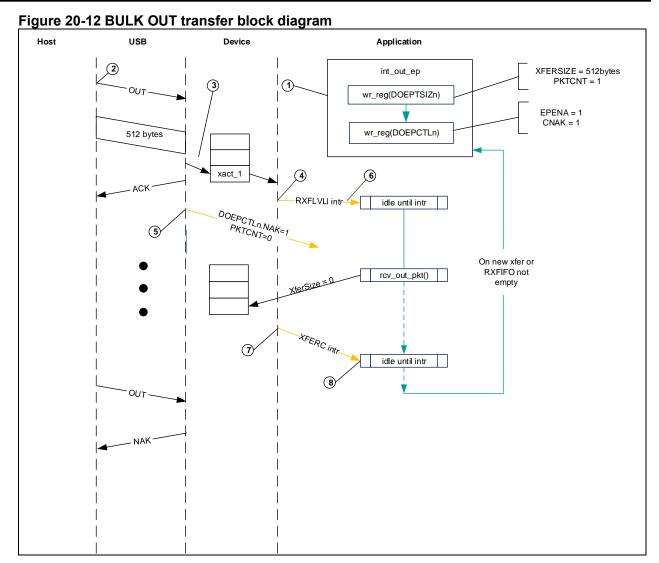

|      | 20.5.4.12        | OUT data transfers                                           | 344       |

|      | 20.5.4.13        | IN data transfers                                            | 346       |

|      | 20.5.4.14        | Non-periodic (bulk and control) IN data transfers            | 347       |

|      | 20.5.4.15        | Non-synchronous OUT data transfers                           | 348       |

|      | 20.5.4.16        | Synchronous OUT data transfers                               | 350       |

|      | 20.5.4.17        | Enable synchronous endpoints                                 | 352       |

|      | 20.5.4.18        | Incomplete synchronous OUT data transfers                    | 353       |

|      | 20.5.4.19        | Incomplete synchronous IN data transfers                     | 354       |

|      | 20.5.4.20        | Periodic IN (interrupt and synchronous) data transfers       | 355       |

| 20.6 | OTGFS control    | and status registers                                         | . 356     |

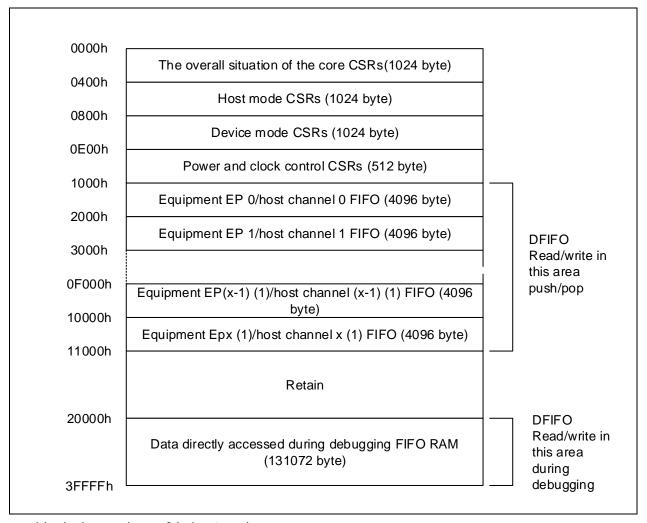

|      | 20.6.1 CSR regis | ster map                                                     | 356       |

|      | 20.6.2 OTGFS re  | egister address map                                          | 358       |

|      | 20.6.3 OTGFS g   | lobal registers                                              | 360       |

|      | 20.6.3.1 O       | TGFS status and control register (OTGFS_GOTGCTL)             | 360       |

|      | 20.6.3.2 O       | TGFS interrupt status control register (OTGFS_GOTGINT)       | 361       |

|      | 20.6.3.3 O       | TGFS AHB configuration register (OTGFS_GAHBCFG)              | 361       |

|      | 20.6.3.4 O       | TGFS USB configuration register (OTGFS_GUSBCFG)              | 362       |

|      | 20.6.3.5 O       | TGFS reset register (OTGFS_GRSTCTL)                          | 363       |

|      | 20.6.3.6 O       | TGFS interrupt register (OTGFS_GINTSTS)                      | 365       |

|      | 20.6.3.7 O       | TGFS interrupt mask register (OTGFS_GINTMSK)                 | 368       |

|      | 20.6.3.8 O       | TGFS receive status debug read/OTG status read and POP i     | egisters  |

|      | (OTGFS_C         | GRXSTSR / OTGFS_GRXSTSP)                                     | 369       |

|      | 20.6.3.9 O       | TGFS receive FIFO size register (OTGFS_GRXFSIZ)              | 370       |

|      | 20.6.3.10        | OTGFS non-periodic Tx FIFO size (OTGFS_GNPTXFSIZ)/E          | ndpoint 0 |

|      | Tx FIFO si       | ze registers (OTGFS_DIEPTXF0)                                | 371       |

|      | 20.6.3.11        |                                                              |           |

|      |                  | GNPTXSTS)                                                    | 371       |

|      |                  | OTGFS general controller configuration register              | 0.70      |

|      |                  | GCCFG)                                                       |           |

|      | 20.6.3.13        | OTGFS controller ID register (OTGFS_GUID)                    | 372       |

|        | 20.6.3.14   | OTGFS host periodic Tx FIFO size register (OTGFS_HPTXI         | FSIZ)372 |

|--------|-------------|----------------------------------------------------------------|----------|

|        | 20.6.3.15   | OTGFS device IN endpoint Tx FIFO size register                 |          |

|        | (OTGFS_DI   | EPTXFn) (x=13, where n is the FIFO number)                     | 373      |

| 20.6.4 | Host-mode   | registers                                                      | 373      |

|        | 20.6.4.1 OT | GFS host mode configuration register (OTGFS_HCFG)              | 373      |

|        | 20.6.4.2 OT | GFS host frame interval register (OTGFS_HFIR)                  | 374      |

|        | 20.6.4.3 OT | GFS host frame number/frame time remaining register            |          |

|        | (OTGFS_HF   | FNUM)                                                          | 374      |

|        | 20.6.4.4 OT | GFS host periodic Tx FIFO/request queue register               |          |

|        | (OTGFS_HP   | PTXSTS)                                                        | 374      |

|        | 20.6.4.5 OT | GFS host all channels interrupt register (OTGFS_HAINT)         | 375      |

|        | 20.6.4.6 OT | GFS host all channels interrupt mask register                  |          |

|        | (OTGFS_HA   | AINTMSK)                                                       | 375      |

|        | 20.6.4.7 OT | GFS host port control and status register (OTGFS_HPRT).        | 375      |

|        |             | GFS host channelx characteristics register (OTGFS_HCCH         | , ,      |

|        | 08, where   | x= channel number)                                             | 377      |

|        |             | GFS host channelx interrupt register (OTGFS_HCINTx) (x =       |          |

|        |             | nannel number)                                                 |          |

|        |             | OTGFS host channelx interrupt mask register (OTGFS_HCI         | •        |

|        |             | here x= channel number)                                        |          |

|        |             | OTGFS host channelx transfer size register (OTGFS_HCTS         | , ,      |

|        |             | x= channel number)                                             |          |

|        |             | de registers                                                   |          |

|        |             | GFS device configure register (OTGFS_DCFG)                     |          |

|        | 20.6.5.2 OT | GFS device control register (OTGFS_DCTL)                       | 380      |

|        |             | GFS device status register (OTGFS_DSTS)                        |          |

|        |             | GFS device OTGFSIN endpoint common interrupt mask reg          |          |

|        |             | EPMSK)                                                         | 382      |

|        |             | GFS device OUT endpoint common interrupt mask register DEPMSK) | 383      |

|        | 20.6.5.6 OT | GFS device all endpoints interrupt mask register               |          |

|        | (OTGFS_DA   | AINT)                                                          | 383      |

|        | 20.6.5.7 OT | GFS all endpoints interrupt mask register (OTGFS_DAINTM        | 1SK)383  |

|        |             | GFS device IN endpoint FIFO empty interrupt mask registe       |          |

|        | (OTGFS_DI   | EPEMPMSK)                                                      | 384      |

|        |             | GFS device control IN endpoint 0 control register              |          |

|        |             | EPCTL0)                                                        |          |